# YILDIZ TECHICAL UNIVERSITY INSTITUTE FOR GRADUATE STUDIES IN SCIENCE AND ENGINEERING

# A 4-GHz SiGe HBT DLL, CONFIGURABLE for SKEW CANCELLATION, MULTIPHASE CLOCKING AND FREQUENCY SYNTHESIZING APPLICATIONS

B.S. Emek GÜNDOĞDU

Electronics and Communication Engineering Department Elecktronics Engineering Programme

M.S. THESIS

Supervisor: Prof. Dr. Atilla ATAMAN

AC. DR. ACC LORISTANBUL, 2004

Aut an Onic BOLAN

# TABLE OF CONTENTS

| LIST OF SYMBOLS                            | i                                      |

|--------------------------------------------|----------------------------------------|

| LIST OF ABBREVATIONS                       | ······································ |

| LIST OF FIGURES                            | v                                      |

| PREFACE                                    | i                                      |

| ABSTRACT                                   |                                        |

| ÖZET                                       |                                        |

| GENİŞLETİLMİŞ TÜRKÇE ÖZET                  |                                        |

|                                            |                                        |

|                                            |                                        |

| 1.1 Motivation                             |                                        |

| 1.3 Thesis Organization                    |                                        |

|                                            |                                        |

| 2 DLL BASICS AND LOOP COMPONENTS           |                                        |

| 2.1 Phase Detectors                        |                                        |

| 2.1.1 Multiplier Type Phase Detectors      |                                        |

| 2.1.2 Sequential Type Phase Detectors      |                                        |

| 2.3 Loop Filters                           |                                        |

| 2.4 Voltage Controlled Delay Line          |                                        |

| 2.4.1 Delay Stages                         |                                        |

| 2.4.2 VCDL Transfer Function               |                                        |

| 2.5 DLL Application Areas                  |                                        |

| 2.5.1 Skew Cancellation                    |                                        |

| 2.5.2 Multiphase Clocking                  |                                        |

| 2.5.3 Frequency Synthesizying              |                                        |

| 2.5.4 Clock and Data Recovery              |                                        |

| 2.5.5 Other Application Areas              | 40                                     |

| 3 DLL DYNAMICS AND NOISE PROPERTIES        | 42                                     |

| 3.1 Small-signal AC Model                  | 44                                     |

| 3.2 Discrete-time Model                    |                                        |

| 3.3 Timing Jitter and Phase Noise          | 51                                     |

| 3.3.1 Introduction                         |                                        |

| 3.3.2 Noise Sources in a Differential Pair |                                        |

| 3.3.3 DLL Noise Consideritions             | 64                                     |

| 4 A 4GHz SiGe HBT DLL DESIGN               | 71                                     |

| 4.1 Phase/Frequency Detector               | 72                                     |

| 4.2 Charge Pump and Loop Filter            |                                        |

| 4.3 Voltage Controlled Delay Line          |                                        |

| 4.3.1 Delay Stage Design                   |                                        |

| 432 Varactor Design                        | 87                                     |

| 4.3.3   | VCDL Design                    | 92  |

|---------|--------------------------------|-----|

|         | esults                         |     |

| 4.4.1   | Stability Analysis in s-domain | 101 |

| 4.4.2   | Jitter Peaking                 | 104 |

| 4.4.3   | Stability Analysis in z-domain |     |

| 4.4.4   | VCDL Output Jitter             | 108 |

| 4.4.5   | Power Comsumption              | 110 |

| 4.4.6   | Operation                      | 111 |

| 5 IMPL  | EMENTATION & TEST              | 113 |

| 5.1 M   | Iaster Bias                    | 114 |

| 5.2 Ec  | dge Combiner                   | 115 |

| 5.2.1   | Digital Edge Combiner          | 116 |

| 5.2.2   | LC Tank                        | 119 |

| 5.2.3   | Conclusion                     | 124 |

| 5.3 Te  | est and Measurement            |     |

| 5.3.1   | Fabricated Stand-alone VCDL    | 125 |

| 5.3.2   | Prototype IC                   | 128 |

|         | NCES                           |     |

| BIOGRAP | PHY                            | 13  |

| 3       |                                |     |

#### LIST OF SYMBOLS

A Ampere f femto F farad H henry G Giga

g<sub>m</sub> Transconductance

$\begin{array}{ccc} \text{Hz} & & \text{Hertz} \\ \text{K} & & \text{Kilo} \\ \text{K}_{\text{VCDL}} & & \text{VCDL gain} \end{array}$

K<sub>PD-CP</sub> Phase detector & charge pump gain

L Length of transistor

m mili

M Mega

n nano

p pico

r<sub>o</sub> Output resistance

s second

t<sub>ox</sub> Oxide thickness

μ Micro

Uo Mobility

V Volt

W Width of transistor

$\begin{array}{ccc} mW & & mili\text{-Watt} \\ \zeta & & Damping factor \\ \omega_n & & Natural frequency \\ \sigma & & standard deviation \\ \sigma^2 & & variance \end{array}$

$\sigma^2$  variance  $\Omega$  Ohm

#### LIST OF ABBREVIATIONS

PLL Phase-Locked Loop

DLL Delay-Locked Loop

IC Integrated Circuit

ADC Analog/Digital Converter CDR Clock and Data Recovery PSD Power Spectral Density

CMRR Common Mode Rejection Ratio VCO Voltage controlled oscillator VCDL Voltage controlled delay line

LP Loop filter

LPF Low pass filter

PD Phase detector

PFD Phase/Frequency detector

CP Charge pump

SNR Signal-to-noise ratio

SNDR Signal-to-noise plus distortion ratio

ENOB Effective number of bits

SFDR Spurious free dynamic range

DNL Differential non-linearity

INL Integral non-linearity

EF Emitter follower

PM Phase Margin

ECL Emitter Coupled Logic

ESD Electrostatic Discharge

CML Current Mode Logic

Gbps Giga bits per second

Gsps Giga samples per second

IEEE The Institute of Electrical and Electronics Engineers, Inc.

I/O Input/ output

LVDS Low Voltage Differential Signalling

PCB Printed Circuit Board

PSRR Power Supply Rejection Ratio

V<sub>PP</sub> Volts peak-to-peak BER Bit Error Rate

MIM Metal-insulator-metal ISI Intersymbol Interference

# LIST OF FIGURES

| Figure 2.1 Basic DLL block diagram                                                     | 4    |

|----------------------------------------------------------------------------------------|------|

| Figure 2.2 Basic PLL block diagram                                                     |      |

| Figure 2.3 Phase detector characteristic in ideal case.                                |      |

| Figure 2.4 Analog multiplier phase detector characteristic for sinusoidal inputs       | 7    |

| Figure 2.5 (a)SR flip-flop phase detector (b) SR flip-flop phase detector operation    |      |

| Figure 2.6 SR flip-flop phase detector characteristic.                                 |      |

| Figure 2.7 Phase/frequency detector.                                                   |      |

| Figure 2.8 PFD operation.                                                              |      |

| Figure 2.9 Phase/frequency detector characteristic                                     |      |

| Figure 2.10 (a) Charge Pump and (b) its operation                                      |      |

| Figure 2.11 PFD dead-zone and corresponding DLL output peak-to-peak jitter             | 15   |

| Figure 2.12 Charge pump and loop filter implementation example                         |      |

| Figure 2.13 Some possible transfer functions for DLL                                   |      |

| Figure 2.14 Phase difference detection range                                           |      |

| Figure 2.15 Voltage controlled delay line block diagram.                               |      |

| Figure 2.16 Passive implementation of VCDL.                                            |      |

| Figure 2.17 Implementation examples of single-ended delay stages.                      |      |

| Figure 2.18 Implementation examples of differential delay stages                       |      |

| Figure 2.19 Formation of "skew" phenomenon in ICs                                      |      |

| Figure 2.20 Reduction of skew with a clock distribution network.                       |      |

| Figure 2.21 DLL used in skew cancellation application.                                 | 28   |

| Figure 2.22 Very high sample rate Flash ADC block diagram with skew cancellation DLLs  | s.29 |

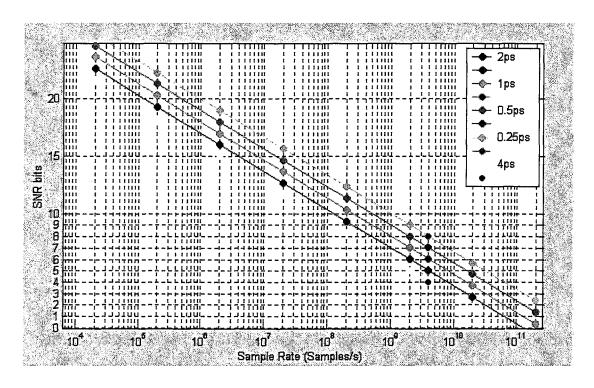

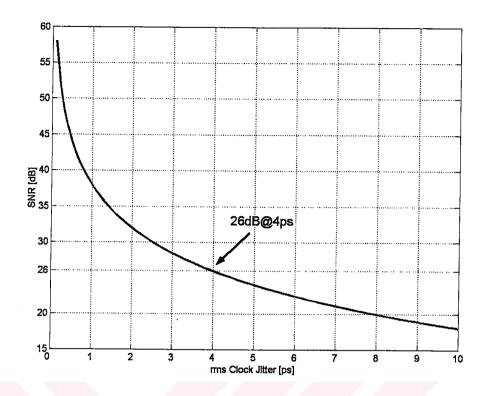

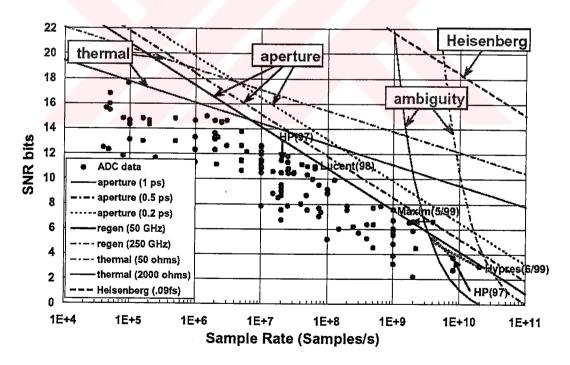

| Figure 2.23 Sampling rate versus ENOB for a given clock jitter in ADCs                 | 31   |

| Figure 2.24 Resolution versus rms clock jitter in ADCs                                 |      |

| Figure 2.25 Resolution versus sample rate for other system imperfections in ADC        |      |

| Figure 2.26 (a) n-way time interleaved ADC with a DLL generating multiphase of the     |      |

| reference clock signal. (b) multiphase clock signal generated by each delay cell of VC | DL.  |

|                                                                                        | 34   |

| Figure 2.27 (a) DLL-based frequency multiplier and (b) its operation                   |      |

| Figure 2.28 Direct conversion receiver block diagram                                   | 37   |

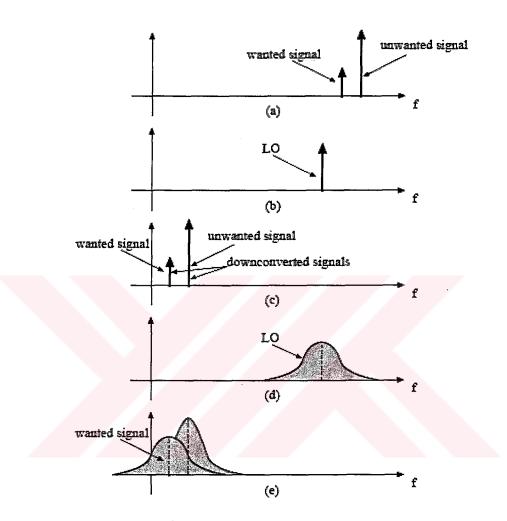

| Figure 2.29 The effect of LO phase noise on downconverted signals.                     |      |

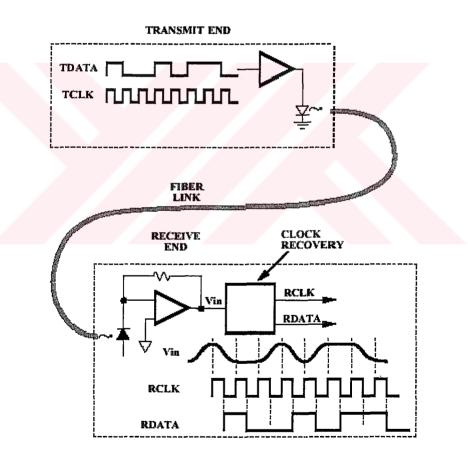

| Figure 2.30 Typical fiber optic serial data transmission system.                       |      |

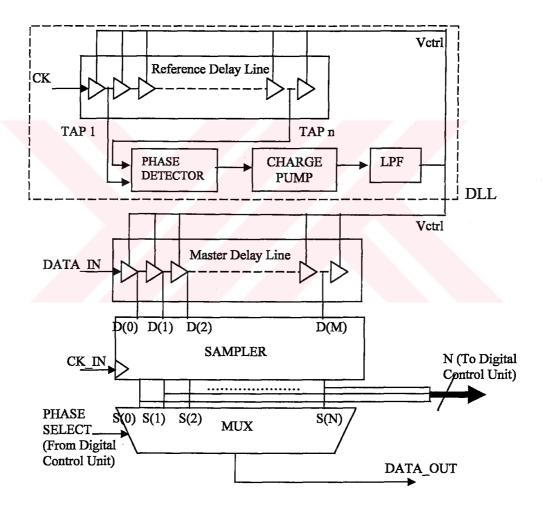

| Figure 2.31 DLL used in CDR application.                                               |      |

| Figure 3.1 Fully "Digital" DLL block diagram                                           |      |

| Figure 3.2 Re-circulating DLL block diagram.                                           |      |

| Figure 3.3 DLL block diagrams (a) Type-I and (b) Type-II                               | 43   |

| Figure 3.4 Type-II DLL in skew cancellation application                                | 44   |

| Figure 3.5 s-domain representation of DLL loop                                         |      |

| Figure 3.6 s-domain representation of DLL with additive noise sources                  | 47   |

| Figure 3.7 Discrete-time model of a DLL                                                |      |

| Figure 3.8 Modified z-domain model of Type-I DLL                                       | 50   |

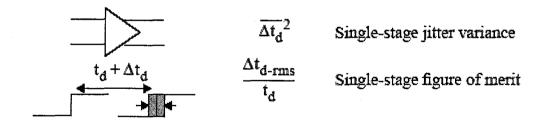

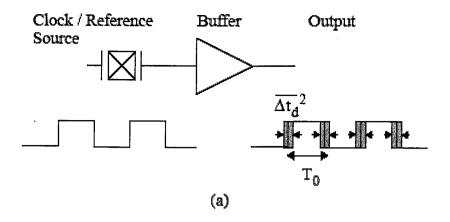

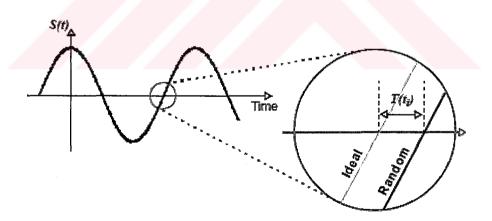

| Figure 3.9 Jitter in time and frequency domain                                         | 52   |

| Figure 3.10 Illustration of timing jitter in an individual delay stage                 | 52   |

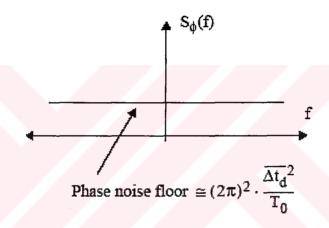

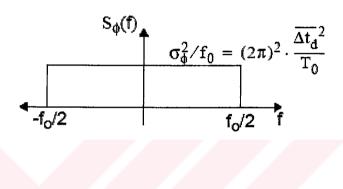

| Figure 3.11 Buffer phase noise spectrum.                                               | 53   |

| righte 2.11 partier britise gorse sheer arm                                            |      |

| Figure 3.12 Timing jitter in clock buffers (a) addition of timing jitter to output signal (b) |            |

|-----------------------------------------------------------------------------------------------|------------|

| resulting output phase noise spectrum                                                         | 55         |

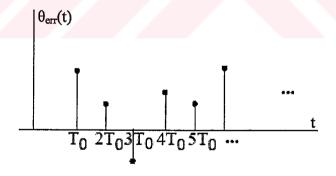

| Figure 3.13 Phase error as a function of time.                                                |            |

| Figure 3.14 Differential pair with representative noise sources                               | 56         |

| Figure 3.15 Timing uncertainties of a sine wave.                                              |            |

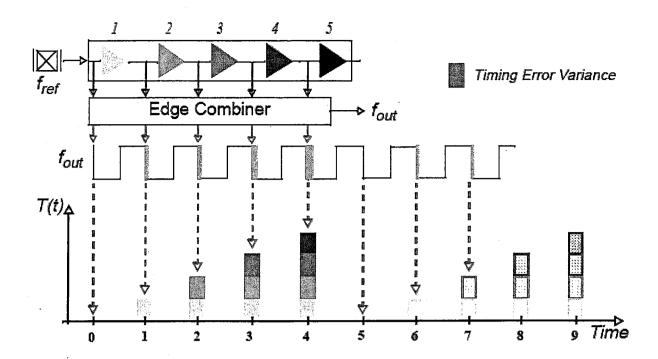

| Figure 3.16 Timing jitter accumulation for Ring Oscillator VCO vs. Delay Chain                | 66         |

| Figure 3.17 Timing jitter accumulation for 5-stage example                                    |            |

| Figure 4.1 Phase/frequency detector block diagram.                                            | 72         |

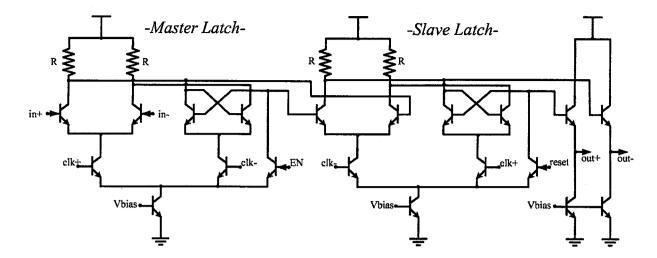

| Figure 4.2 Master-slave DFF.                                                                  | 73         |

| Figure 4.3 Input buffer cirtcuit schematic.                                                   |            |

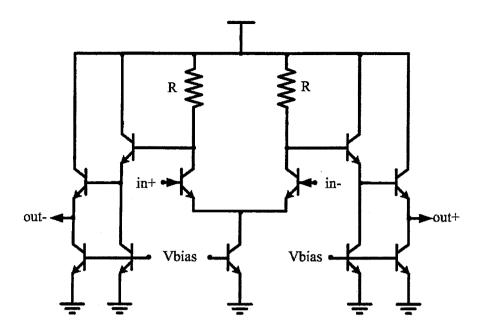

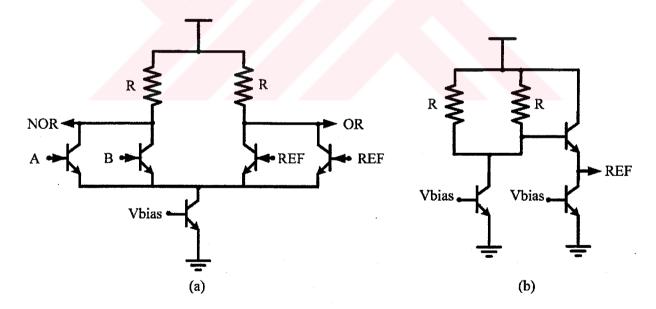

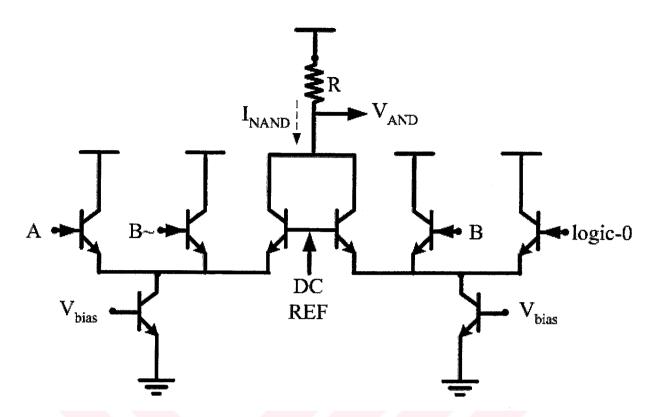

| Figure 4.4 (a) OR gate schematic and (b) its DC reference generator                           | 75         |

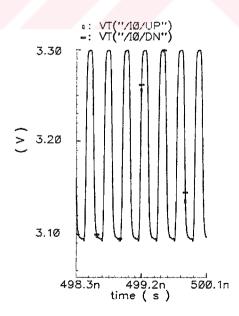

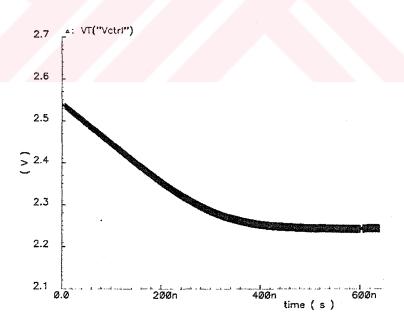

| Figure 4.5 Simulation example for up and down signals in locked condition                     | 76         |

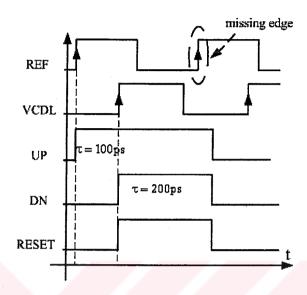

| Figure 4.6 Nonideal behavior of PFD caused by increased reset path delay                      | 77         |

| Figure 4.7 Phase/frequency detector characteristic experiencing zero dead-zone                | 78         |

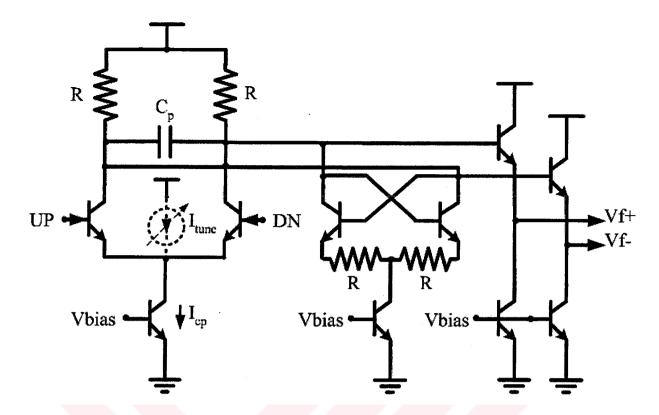

| Figure 4.8 Charge pump schematic                                                              | 79         |

| Figure 4.9 Charge Pump output stage                                                           | 80         |

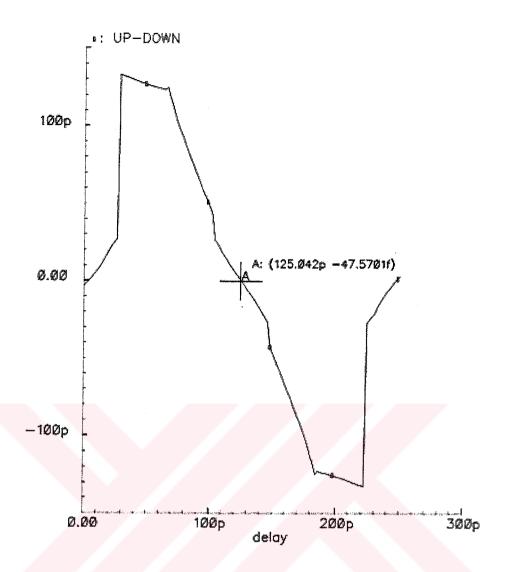

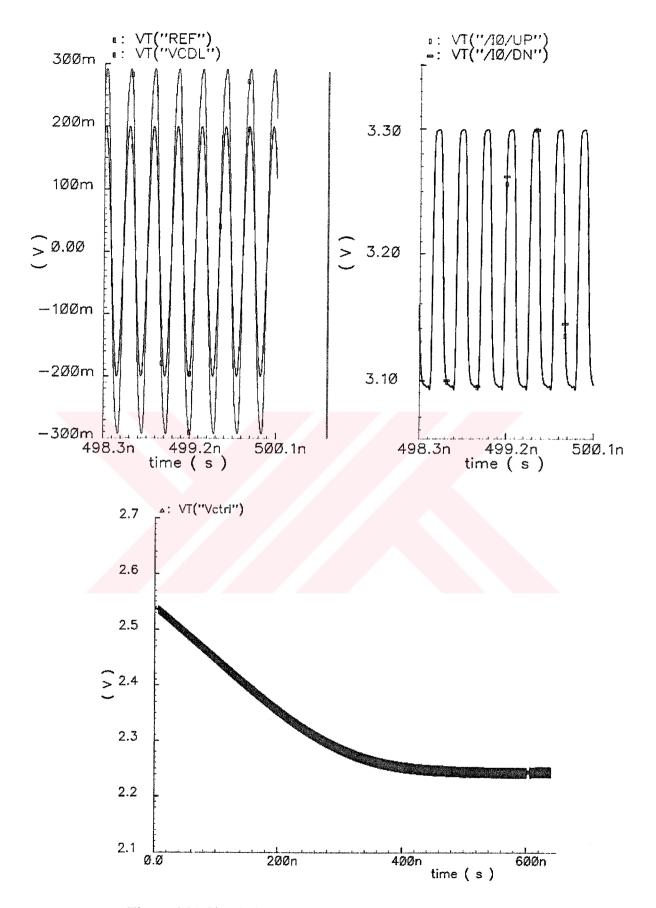

| Figure 4.10 Control voltage versus simulation time                                            |            |

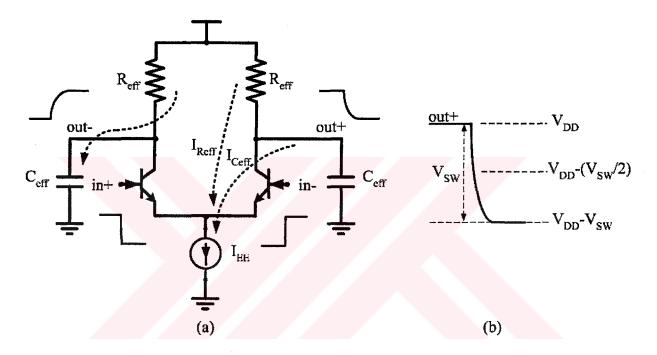

| Figure 4.11 Emitter-Coupled stage dynamic behavior                                            | 82         |

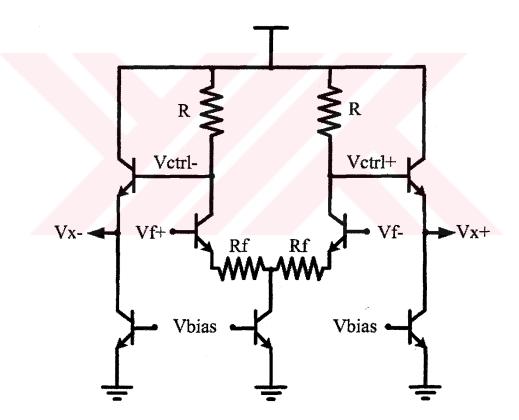

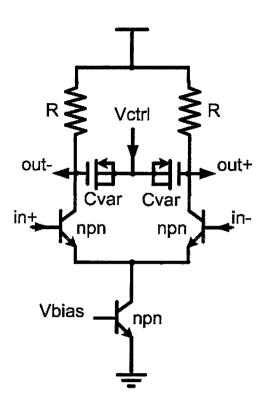

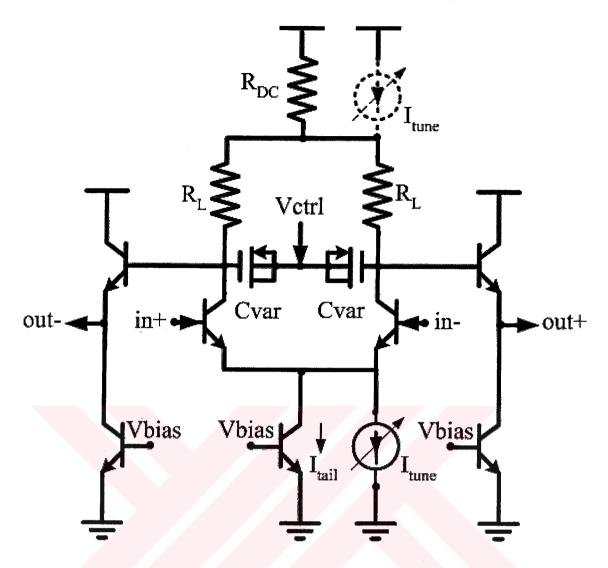

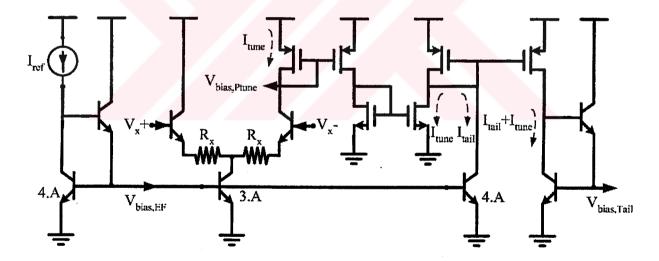

| Figure 4.12 Delay stage schematic                                                             |            |

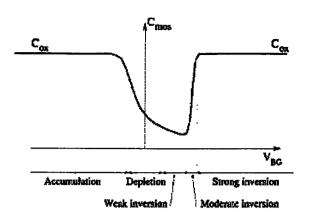

| Figure 4.13 Tuning characteristics for the PMOS capacitor with bulk, drain and source         |            |

| terminals shorted (B≡D≡S).                                                                    | 88         |

| Figure 4.14 Charge carrier path for PMOS capacitor working in the strong and moderate         |            |

| inversion regions (solid lines) and in the depletion and accumulation regions (dashed         |            |

|                                                                                               | 88         |

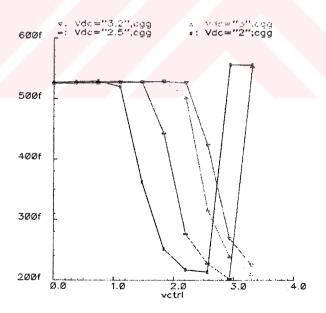

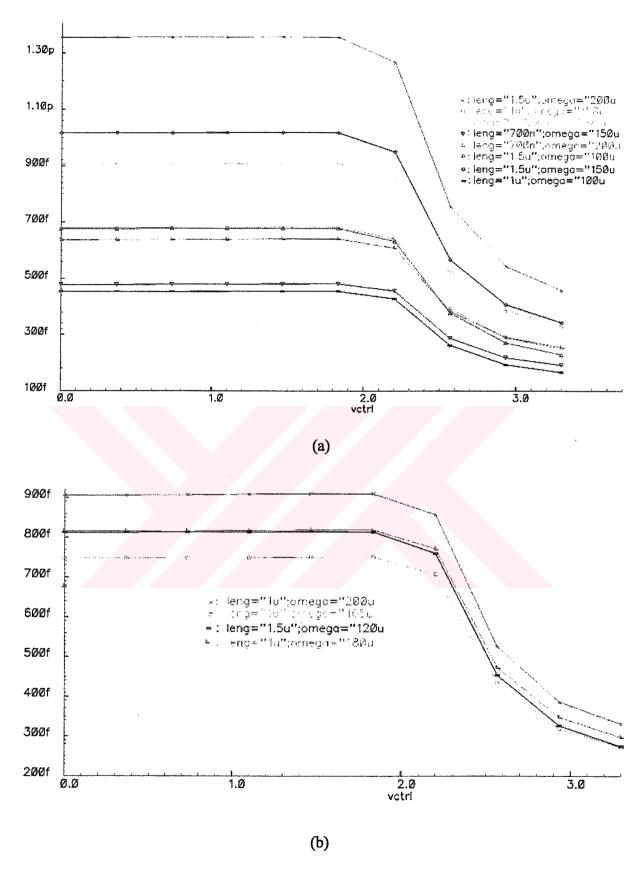

| Figure 4.15 capacitance vs control voltage for different gate voltage biasings                |            |

| Figure 4.16 Capacitance vs control voltage with different channel lengths                     |            |

| Figure 4.17 Basic delay stage                                                                 |            |

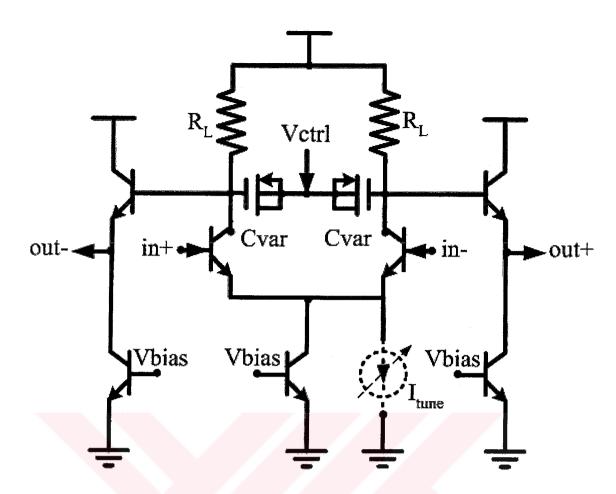

| Figure 4.18 Modified delay stage.                                                             |            |

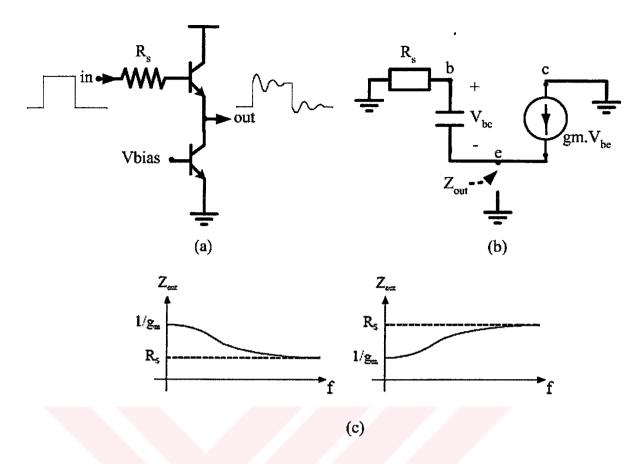

| Figure 4.19 Ringing phenomenon (a) an emitter follower experiencing ringing on the outp       | out        |

| signal (b) small-signal equivalent of emitter follower (c) output impedence vs frequen        |            |

| for R <sub>s</sub> <r<sub>e and R<sub>s</sub>&gt;r<sub>e</sub> respectively</r<sub>           |            |

| Figure 4.20 Delay stage implementation.                                                       |            |

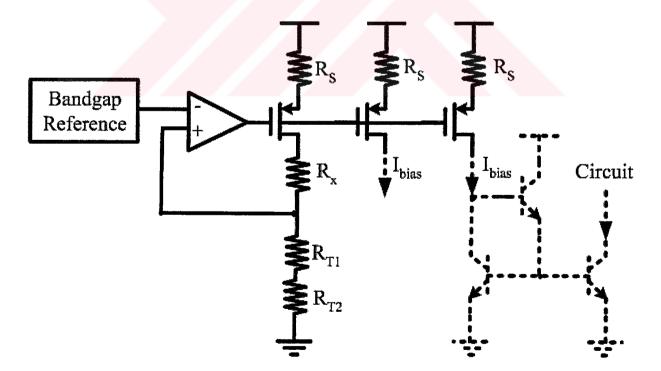

| Figure 4.21 Voltage controlled delay line biasing scheme.                                     |            |

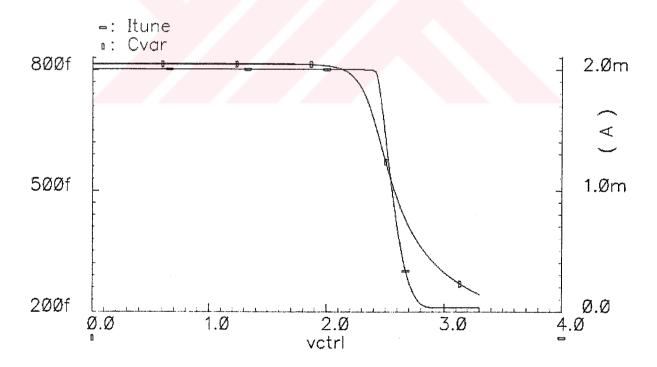

| Figure 4.22 Tuning current and varactor capacitance versus control voltage                    |            |

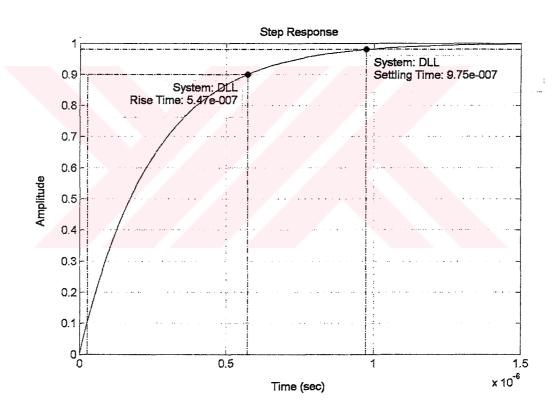

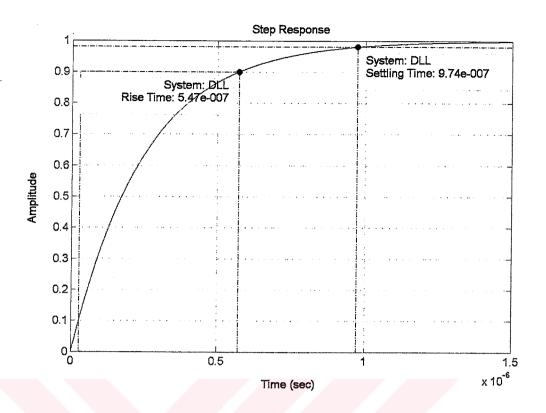

| Figure 4.23 Step response of the DLL s-domain model                                           |            |

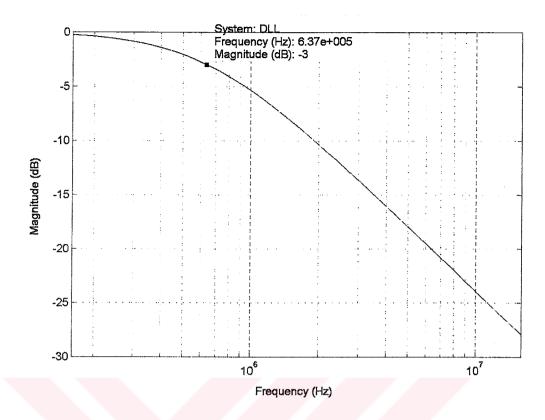

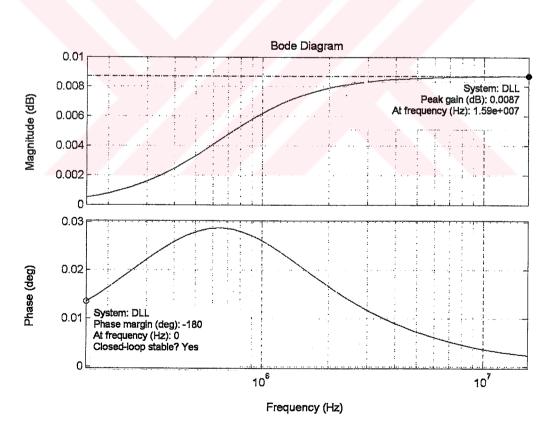

| Figure 4.24 Bode plot of the DLL s-domain model                                               |            |

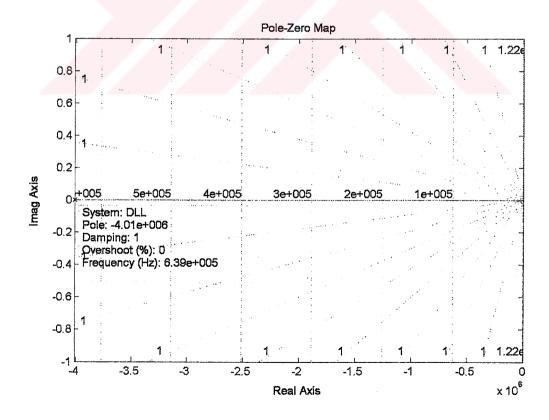

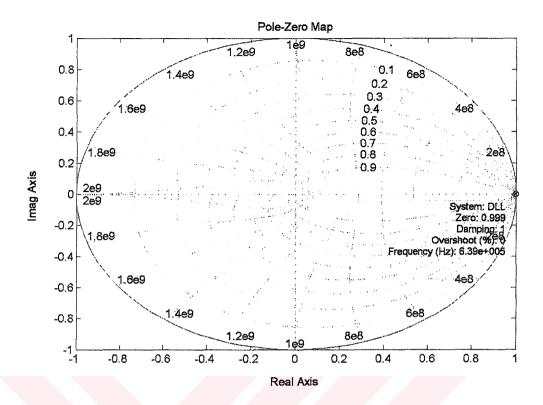

| Figure 4.25 Zero-Pole map of the DLL s-domain model                                           |            |

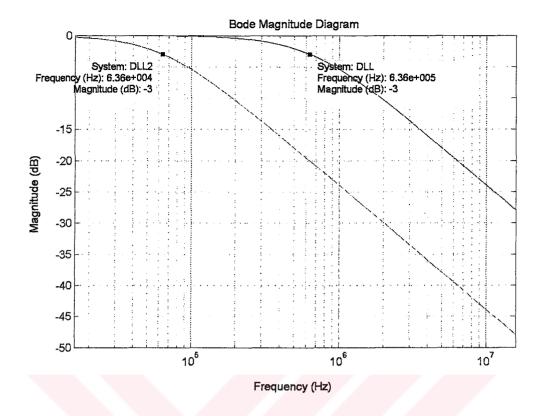

| Figure 4.26 Bode plots of DLL s-domain model for I <sub>cp</sub> 1mA (DLL) and 0.1mA (DLL2)   |            |

| Figure 4.27 Jitter transfer of the DLL                                                        |            |

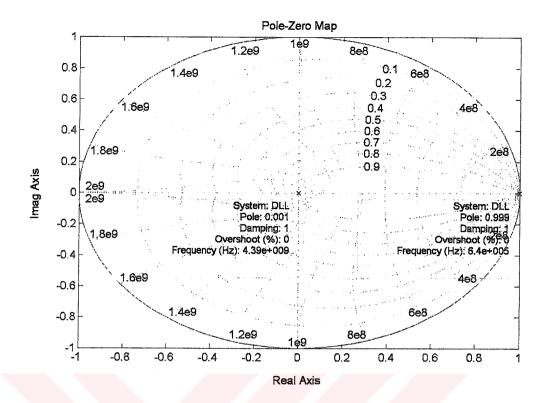

| Figure 4.28 Zero-Pole map of the DLL.                                                         |            |

| Figure 4.29 Step response of DLL z-domain model                                               |            |

| Figure 4.30 Bode plots of DLL z-domain model                                                  |            |

| Figure 4.31 Zero-Pole map of DLL z-domain model                                               |            |

| Figure 4.32 Simulation example for locked condition of DLL                                    |            |

| Figure 5.1 Master bias circuit.                                                               |            |

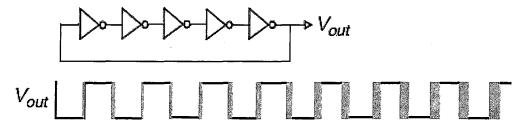

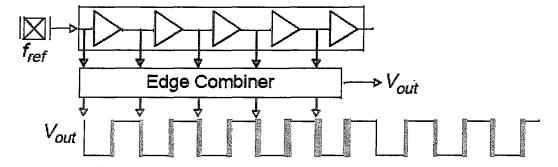

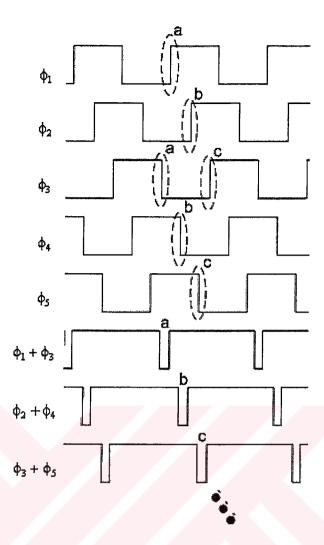

| Figure 5.2 Digital edge combiner operation                                                    |            |

| Figure 5.3 Current mode NAND gate schematic                                                   |            |

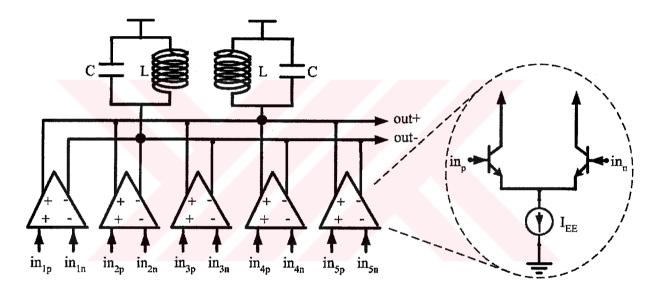

| Figure 5.4 Edge combiner for five stage example with differential output                      |            |

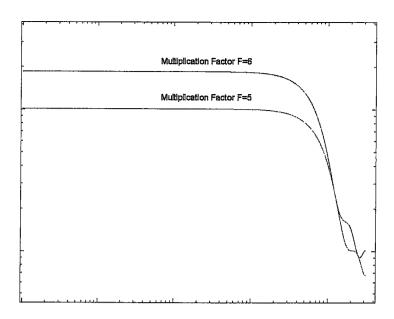

| Figure 5.5 PSD plots for F=5 and F=6                                                          |            |

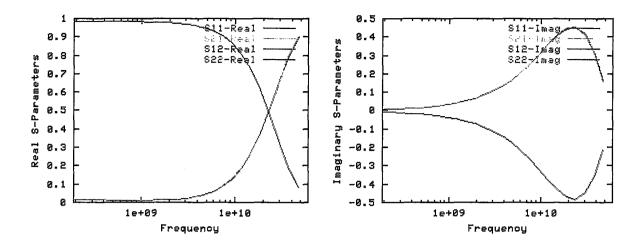

| Figure 5.6 Scattering parameters of designed inductor                                         |            |

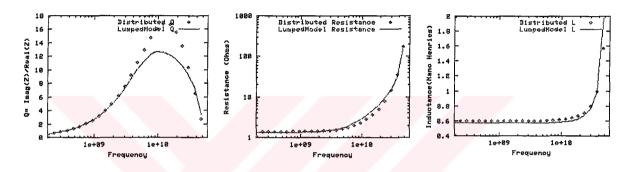

| Figure 5.7 Comparison for distributed and lumped inductance models for L=600nH                | $\pm 12.1$ |

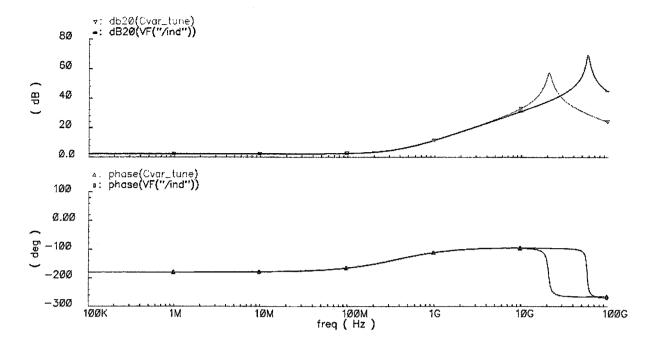

| Figure 5.8 AC behavior of the inductor and inductor tuned with a varactor | 122 |

|---------------------------------------------------------------------------|-----|

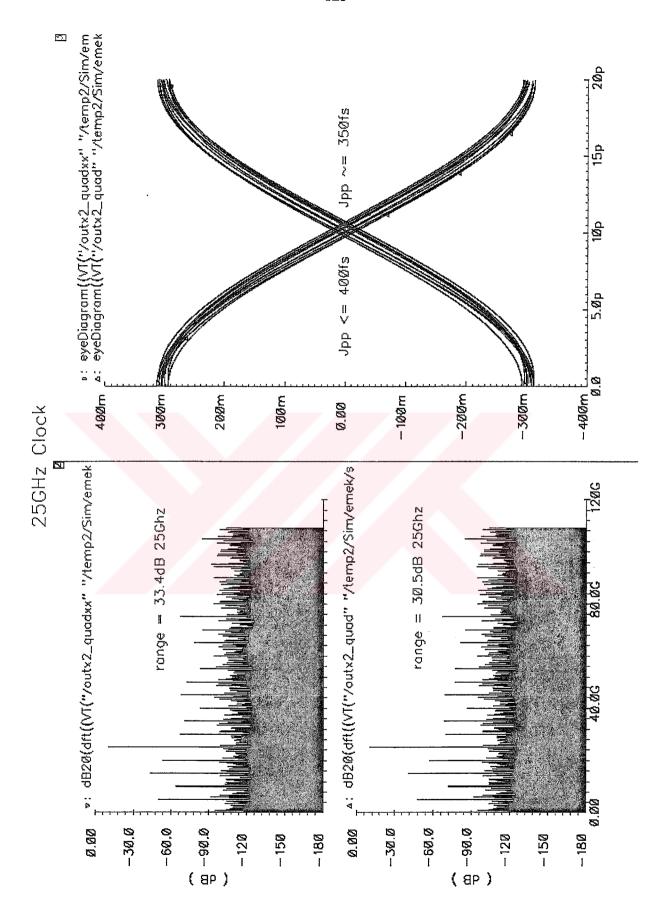

| Figure 5.9 Simulation example for 5×5GHz case edge combiner output        | 123 |

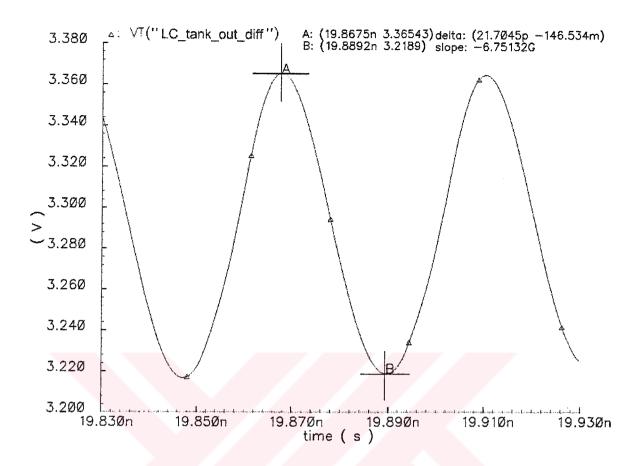

| Figure 5.10 6×4GHz case LC tank differential output                       | 124 |

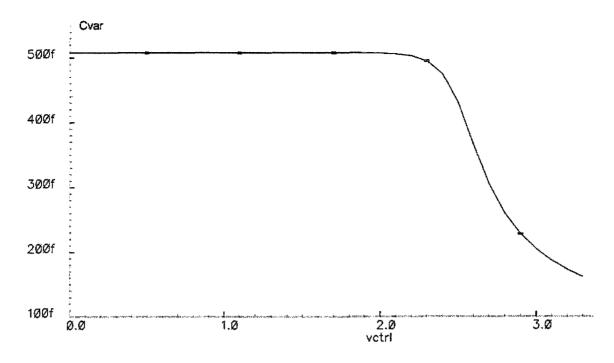

| Figure 5.11 Varactor tuning curve used in fabricated VCDL                 | 126 |

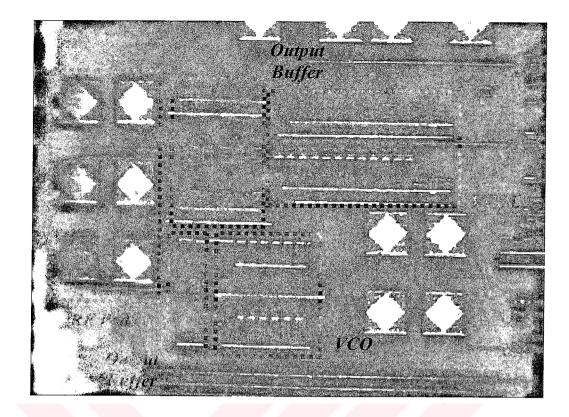

| Figure 5.12 Stand-alone VCDL and VCO die photo                            |     |

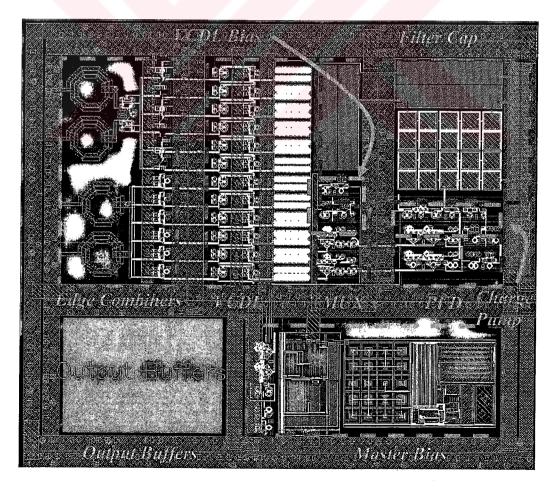

| Figure 5.13 Prototype IC toplevel layout                                  |     |

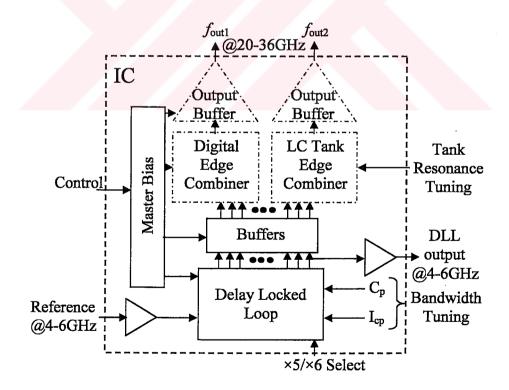

| Figure 5.14 Prototype IC block diagram                                    |     |

#### **PREFACE**

First, I would like to thank my thesis advisor Prof. Dr. Atilla Ataman for his assistance and support during this work, and take a chance of working together within the future works hopefully.

I would like to thank my colleagues in ITU-ETA ASIC Design Center who have guided me with valuable advices and technical discussions.

I am grateful to my friends for baring me and my darling for her patience and support during the documentation of the work.

Finally I dedicate my thesis to my lovely family.

#### **ABSTRACT**

Synchronization and skew problems become more important as the modern electronic communication systems' operating frequencies increase. Delay Locked Loop (DLL), a first order feedback system, has been analyzed theoretically in comparable approach with PLLs and designed to operate at 4GHz and up to 6GHz clock signals for skew cancellation and multiphase clocking applications. In order to exploit DLLs' unique features, additional edge combiner circuitries have been designed in order to be able to synthesize up to 36GHz output clock signal.

Core DLL and additional circuitries are designed in 0.35µm SiGe HBT BiCMOS technology. High speed circuit techniques and high speed transistor fabrication techniques are investigated from noise features point of view, in order to lead excellent noise properties of DLLs to the edge. Thus, skew cancellation DLL output jitter is found to be 2.5ps peak-to-peak in analytical calculations (without edge combiners), and will be verified in prototype IC measurements.

Keywords: DLL, skew cancellation, frequency synthesizer, jitter, phase noise

#### JURY:

1. Prof.Dr. Atilla ATAMAN (Supervisor) Date: 14.07.2004

2. Prof.Dr. Oruç BİLGİN Page: 150

3. Doç.Dr. Ali ZEKİ

#### ÖZET

Modern elektronik haberleşme devrelerinin çalışma frekansları arttıkça, sekronizasyon ve istenmeyen saat işaret gecikmesi (skew) problemlerinin önemi artmaktadır. Senkronizasyon (skew cancallation) ve çok fazlı saat işareti kullanılan uygulamalarda kullanılmak üzere, birinci dereceden geribeslemli kontrol sistemi olan Gecikme Kilitlemeki Çevrim (DLL) devrelerinin teorik analizleri, Faz Kilitlemeli Çevrim (PLL) devreleriyle karşılaştırmalı olarak yapılmış ve 4GHz den 6GHz saat işareti frekanslarına kadar çalışabilecek şekilde tasarlanmıştır. Ayrıca DLL devrelerinin sağladığı avantajlardan sonuna kadar yaralanabilmek için 36GHz frekansına kadar ulaşabilen saat işaretlerini sentezleyen "kenar birleştirici (edge combiner)" devreler tasarlanmıştır.

Çekirdek DLL ve ek devreler 0.35µm SiGe HBT BiCMOS teknolojisi kullanılarak tasarlanmıştır. DLLlerin mükemmel gürültü özelliklerinin, sınırlarına kadar kullanılabilmesi için, yüksek hızlı devre teknikleri ve yüksek hızlı transistör üretim teknikleri, gürültü özellikleri bakımından incelenmiştir. Böylece, analitik hesaplamalarda, senkronizasyon için kullanılacak DLL'in çıkış titremesi tepeden tepeye 2.5ps olarak hesaplanmıştır ve bu sonuç prototip tümdevresinin ölçümleriyle doğrulanacaktır.

Anahtar Kelimeler: DLL, senkronizasyon, frekans sentezleyici, titreme, faz gürültüsü

#### лïкi:

1. Prof.Dr. Atilla ATAMAN (Danışman)

2. Prof.Dr. Oruç BİLGİN

3. Doç.Dr. Ali ZEKİ

Kabul tarihi: 14.07.2004

Sayfa sayısı: 150

### GENİŞLETİLMİŞ TÜRKÇE ÖZET

Son yıllarda, modern haberleşme elektroniği sistemlerinde veri iletim hızlarının ve dolayısıyla çalışma frekanslarının artması, verinin güvenilir hata oranlarında iletilmesi problemini doğurmaktadır. Düşük BER değerlerine erişebilme hedefi, yüksek frekanslı saat ve veri işaretlerinin gürültü özelliklerinin, alışageldik devre çözümlerinde elde edilebilenlere göre oldukça iyileştirilmesini gerekli kılmaktadır. Çoğunlukla mikroişlemciler, DSP ve sayısal devreler içerisinde istenmeyen gecikme problemlerinin üstesinden gelebilmek üzere kullanılagelen Gecikme Kilitlemeli Çevrim (Delay Locked Loop: DLL) yapılarının mükemmele yakın gürültü performansları, DLL yapılarının yüksek frekans bölgesinde çeşitli amaçlar için kullanılmasını gündeme getirmiştir.

DLL yapıları geri-beslemeli bir kontrol sistemidir. DLL, girişine uygulanan saat işaretini, gerilim kontrollü geciktirici hat (Voltage Controlled Delay Line: VCDL) yardımıyla geciktirmektedir ve ne kadar geciktireceği ise bir kontrol çevrimiyle belirlenmektedir. Geri besleme çevrimi, referans işaret ile VCDL çıkışındaki geciktirilmiş işaretin faz farklarının hesaplandığı faz dedektörü, hesaplanan faz farkı bilgisine göre VCDL'in kontrol işaretinin üretildiği yük pompası ve kontrol işareti üzerindeki yüksek frekanslı bileşenlerin süzüldüğü çevrim filtresinden oluşmaktadır [Bölüm-2 Şekil 2.1]. Yük pompasının kullanımı seçilecek faz dedektör topolojisine bağlıdır ve en genel halde DLL yapılarında kullanılmayabilir. DLL'de kilitlenme ise şu şekilde elde edilir; faz dedektörü herbir referans ve çıkış işaret periyodlarında yeni bir kıyaslama yaparak kontrol işaretinin bir sonraki değerini belirler iken, VCDL bu kontrol işaretine uygun yeni gecikme miktarını referans işaretine ekleyerek çıkış işaretini üretir. Böylece, kullanılan negatif geri besleme yardımıyla, VCDL'in çıkışındaki geciktirilmiş işaret yani DLL'in çıkış işareti ile giriş işareti yani referans arasında sıfır faz farkı elde edilmiş olur. DLL'in kilitlendiği durumda referans işareti ile çıkış işaretinin arasındaki faz farkının sıfır olması, tümdevre üzerinde saat işareti dağıtımı yapılırken farklı noktalarda ortaya çıkan istenmeyen gecikmelerin (skew) ortadan kaldırılmasında kullanılabileceğini göstermektedir. Bu istenmeyen gecikmeler, tümdevre üzerinde saat işaretinin dağıtılması esnasında farklı noktalara ulaşırken, eşit olmayan parazitik etkilere maruz kalması ve/veya eşit olmayan sayıda sürücü devreler kullanılması sonucu ortaya çıkabilmektedir. Bunların neticesinde istenmeyen gecikme değerleri büyük miktarlara ulastığı takdirde, eşit yollar/sürücü sayısı gibi basit çözümler yetersiz kalmakta ve DLL gibi aktif devre çözümleri kaçınılmaz olmaktadır. DLL'in istenmeyen gecikmeleri ortadan kaldırması

sayesinde tümdevre üzerinde farklı noktalarda bulunabilecek, saat işareti kullanan devrelerin senkron çalışmaları sağlanabilecektir. Dolayısıyla DLL yapılarının en temel uygulama alanı, sayısal sistemlerde senkronizasyon ya da gecikme engelleme (skew cancellation) olarak ortaya çıkmaktadır.

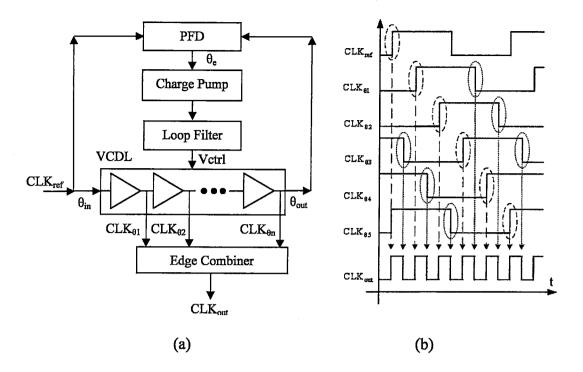

DLL'de kilitlenmenin gerçekleştiği durumda yani giriş işareti ile çıkış işareti arasındaki faz farkı sıfır iken, pratikte VCDL'i oluşturacak devrelerin sıfır gecikme sağlayamayacağı hatırlandığında, toplam VCDL gecikmesi referans işaret periyodunun tam katları olmak zorundadır. Genel halde VCDL gerçeklenirken, minimum gecikmesi referans işaretinin bir periyodundan az tutularak ve ayarlanabilir gecikme miktarı ise referans işaretin en az bir periyodu olmak kaydıyla, kilitlenmenin sağlandığı durumda toplam VCDL gecikmesinin referans işaretinin bir periyodu kadar olması sağlanmaktadır. Pratikte VCDL'in tek bir birim devre ile gerçeklenmesi, istenilen ayarlanabilir gecikme miktarlarının (en az referans işaretin bir periyodu kadar) elde edilmesindeki zorluklardan ötürü mümkün olamamaktadır. Dolayısıyla VCDL birden çok geciktirici kat yardımıyla oluşturulur. Geciktirici katların özellikleri yukarıda belirtilen VCDL'in istenilen özelliklerine göre belirlenmelidir. DLL kilitlenmeyi, referans giriş işareti ile VCDL'de bulunan son katın çıkış işaretine göre sağladığından VCDL'i oluşturan herbir katın aynı miktarda gecikmeye sahip olması yanı eş olması, senkronizasyon için kullanılacak DLL yapılarında gerekli değildir. Ancak VCDL birbirlerine es birim geciktirici katlardan olusturulduğunda, DLL kilitlenmis konumda iken, referans işaretin bir periyodu kadar olan VCDL'in toplam gecikmesi, herbir geciktirici kat çıkışında eşit olarak bölünmüş halde elde edilmiş olacaktır. Örnek olarak VCDL on adet geciktirici kat ile oluşturulduğunda, DLL kilitlendiğinde, herbir geciktirici kat çıkışında referans işaretin, on adet eşit faz farklarıyla ayrılmış halleri bulunacaktır. Bu eşit faz farkına sahip saat işaretleri, çok fazlı saat işaretine (multiphase clocking) ihtiyaç duyan özellikle zaman-paylaşımlı (time-interleaved) uygulamalar için kullanılabilmektedir. Ayrıca eşit gecikme değerleri ile bölmelenmiş referans saat işaretlerinin uygun şekilde birleştirilmesiyle (örneğin herbir geciktirici kat çıkış işaretlerinin yükselen kenarlarının birleştirilmesi), yüksek frekanslı saat işareti sentezlenebilmektedir. On adet geciktirici kat ile oluşturulan VCDL'in kullanıldığı DLL örneği için kilitlenmiş durumda, kenar birleştirici devrenin çıkışında referans işaret frekansının on katı frekansına sahip çıkış işareti üretilebilecektir. DLL'i oluşturan altblokların özellikleri ve DLL'in kullanım alanları ayrıntılarıyla bölüm-2'de açıklanmıştır.

Son yıllarda DLL yapılarının, özellikle GSM-1.8GHz sistemleri için yüksek frekans sentezleme uygulamalarında kullanıldığı ve gürültü özelliklerinin bu uygulamalar için incelendiği literatürde görülmektedir. DLL tabanlı frekans sentezlevicilerin, ring-osilatör kullanan PLL tabanlı frekans sentezleyicilere göre daha iyi gürültü özelliklerine sahip olmasının temel sebebi, titreme (jitter) olarak ortaya çıkan gürültünün, sürücü katların çevrim haline getirilmesiyle oluşturulan ring-osilatörde herbir saat işareti kenarında kümülatif olarak artması (jitter accumulation), DLL yapılarında ise ring-osilatör yerine kullanılan ve kaskad bağlı geciktirici katlardan oluşturulan VCDL'de gürültünün işarete herbir kat için bir kere eklenmesi ve döngü içerisinde kümülatif olarak eklenmemesidir. Dolayısıyla DLL tabanlı frekans sentezleyicileri, ring-osilatör kullanan PLL yapılarına göre daha düşük titremeye sahip yüksek frekanslı saat işaretinin üretilmesini sağlamaktadir. Ring-osilatörlerin kötü titreme performansının özellikle yüksek frekanslı saat işaretlerinin sentezlenmesinde kabul edilebilir sınırların dışına çıkması sebebiyle, PLLlerde LC osilatör kullanılması gerekli olmaktadır. LC osilatörlerin faz gürültüsü (phase noise) performansı rezonans tankında kullanılacak endüktans ve kapasite elemanlarının kalite faktörlerine (Q) doğrudan bağlıdır. İstenilen özelliklere sahip kapasite elemanlarının, günümüz üretim teknolojilerinde, tümdeyre üzerinde gerçeklenmeleri mümkün iken, endüktans elemanlarının tümlestirilmesinde çesitli sorunlar bulunmaktadır. Tümleşik endüktans elemanlarının büyük silikon alanı kaplaması ve tabana olan kaçak akımlar yüzünden ancak düşük kalite faktörlü olarak gerçeklenebilmesi, istenilen titreme/faz gürültüsü performansına ulaşılmasını zorlaştırmaktadır. Bu yüzden DLL tabanlı frekans sentezleyiciler, günümüzde ihtiyaç duyulan düşük titreme performansına sahip yüksek frekanslı saat işaretlerinin elde edilmesine olanak vermektedir.

DLL tabanlı frekans sentezleyicilerin, PLL tabanlı sentezleyicilere göre en önemli dezavantajı, frekans çarpma oranının VCDL'de kullanılan geciktirici kat sayısı tarafından belirlenmesidir. Kullanılacak geciktirici kat sayısının belirlenmesi esnasında, VCDL'den beklenen özellikler ve istenilen frekans çarpma oranı arasında bir çelişki bulunmaktadır. Pratik gerçeklemelerde geciktirici kat sayısı en fazla yüz adete ulaşabilmektedir ancak çalışma frekansları daha da arttığında bu sayı ancak on adet mertebelerindedir. Oysa PLLler oldukça yüksek frekans çarpma oranlarına ulaşabilmektedir. Bu özellikleri sebebiyle PLLler referans işareti olarak, düşük frekanslı ancak oldukça iyi gürültü özelliklerine sahip kristalleri kullanabilmektedir. DLLlerde ise kristallerden daha yüksek frekanslı referans saat işaretinin kullanılması zorunluluğu, daha gürültülü olan referans işaretinin çıkış işareti üzerindeki etkilerinin mümkün olduğunca küçük tutulmasını gerekli kılmaktadır. Aksi takdirde DLLlerin

mükemmel olarak nitelendirilebilecek gürültü özelliklerinin avantajları kaybedilmiş olacaktır. DLLlerin kendi iç gürültüsünün ve referans işaretindeki gürültünün çıkış işaretine etkileri bölüm-3'te incelenmiştir.

Yüksek performanslı tümdevrelerde, istenmeyen gecikmeler (skew) ve senkronizasyon sorunları, çalışma frekansları gigahertz ve üzerine çıktıkça daha da büyük sorun teşkil etmektedir. Bu çalışma frekansı mertebelerinde, işaret iletim hatlarının parazitik direnç ve kapasite etkilerinin yanısıra parazitik endüktans etkileri de ortaya çıkmaktadır. Dolayısıyla düşük frekans uygulamalarında göz ardı edilebilen bir kısım parazitik etkiler ya da birinci dereceden parazitik eleman modellerine dayalı olarak geliştirilen çözüm önerileri (serim teknikleriyle eş uzunluktaki yollar ve/veya saat işareti dağıtım mimarileri gibi), gigahertz üzerindeki çalışma frekanslarında yeterli olamamaktadır. Dolayısıyla işaret hatlarının parazitik etkilerinin dağılmış olarak modellenmesi ve düşük gürültü özelliklerine sahip aktif devreler yardımıyla senkronizasyonun sağlanması zorunluluk olmaktadır. Bu aktif devreler PLL veya DLL olmalıdır ancak PLLlerin kötü gürültü performansı sebebiyle DLL tercih edilmelidir.

Yapılan çalışma 4GHz frekansındaki saat işaretleriyle çalışacak ve senkronizasyon amacıyla kullanılacak bir DLL tasarımıdır. Bölüm-2'de anlatılan DLL altbloklarının özellikleri, bölüm-3'te açıklanan sistem seviyesi kararlılık ve gürültü performansı uyarınca sistem tasarlanmıştır. Faz karşılaştırıcı olarak ölü-bölgesi (dead-zone) olmayan Faz/Frekans Dedektörü, yeni bir yük pompası ve buna bağlı çevrim filtresi ile oniki adet geciktirici kattan oluşan VCDL tasarlanmıştır. VCDL'i oluşturan geciktirici katların gecikme ayarı, herbir katın çıkışındaki kapasitif yükün, ayarlı kapasite elemanı olan varaktörler ile belirlenmesi sağlanarak yapılmaktadır. DLL'in gürültü duyarlılığını azaltmak üzere, sistemde yer alan bloklar diferansiyel işaretler ile çalışacak biçimde tasarlanmıştır. Bunun tek istisnası, VCDL'de yer alan varaktör elemanlarının tek uçlu kontrol gerilimine ihtiyaç duymaları sebebiyle, çevrim filtresinin çıkışında oluşturulan diferansiyel kontrol işareti, tek uçlu hale dönüştürülmesidir.

Bölüm-4'te DLL'i oluşturan herbir altbloğun tasarımlarının yanısıra DLL sisteminin bir araya getirilmesi, yapılan serim sonrası simulasyon sonuçlarıyla birlikte anlatılmaktadır. DLL, PVT (Process, Voltage, Temperature) saçılım köşe durumlarında çalışacak şekilde tasarlanmıştır. Proses saçılmaları uç koşulları üretici firmadan alınmış (yüksek hız, düşük hız, yüksek β, düşük β durumlarının ikili kombinasyonları), besleme gerilimi uç noktaları 3V-3.6V ve çalışma sıcaklık aralığı -20°C ile +130°C olarak seçilmiştir. İlgili bölümün sonuç kısmında, tasarımı tamamlanan DLL'in fonksiyonelliği, kararlılık ve gürültü performansları gerek serim

sonrası simulasyon sonuçları gerekse analitik hesaplama neticileri ile sunulmuştur. Ayıca DLL içerisinde kullanılan herbir kutuplama akım kaynağının referansları, band-aralığı referansından faydalanarak PVT değişimlerinden en az etkilenecek biçimde üreten bir kutuplama merkezinden sağlanmaktadır. Bu birim, ayrıca tasarlanan test bloklarıyla birlikte bölüm-5'te ele alınmaktadır.

Tasarlanan 4GHz frekansında çalışan DLL'den, frekans sentezleyici ve çok fazlı saat isareti üretici olarak da araştırma amaçlı faydalanabilmek için VCDL'i oluşturan geciktirici katlara ek özellikler ilave edilmiştir. Dolayısıyla tasarımda güç harcaması birinci etken olarak göz önüne alınmamıştır. Özellikle frekans sentezleyici olarak DLL'in ve kenar birleştirici olarak çalışabilecek farklı devre yapılarının performanslarının kıyaslanabilmesi için iki adet kenar birleştirici yapı da test amaçlı tasarlanmıştır. VCDL ile kenar birleştirici bloklar arasına tamponlar eklenerek, DLL'in ek test bloklarından en az seviyede etkilenmesine calısılmıstır. DLL'in 6GHz'e kadar güvenilir çalışması sağlanarak, frekans konfigürasyonunda çıkış işaret frekansının 4GHz×5 ile 6GHz×6 aralığında ayarlanabilir olması sağlanmıştır. Çarpma faktörü olan 5 veya 6'nın seçimi, yüksek performanslı bir multiplexer yardımıyla geri-besleme noktasının belirlenmesiyle sağlanmaktadır. Ancak elde edilen en yüksek 36GHz civarındaki çıkış işaretlerinin kuvvetlendirilmesi ve tümdevre dışarısına alınmasında, özellikle bağlantı adalarının (bonding pad) ve seçilecek paketin bandgenişliği sınırlamaları sebebiyle sorun bulunmaktadır. Bu sorunların üstesinden gelebilmek üzere eş zamanlı olarak, endüktif olarak bandgenişliği arttırılan (inductive peaking) çıkış sürücü katın tasarımı, uygun genişbandlı ESD korumalı bağlantı adası tasarımı ve yüksek frekanslarda çalışmaya uygun paket seçimi çalışmaları devam etmektedir. Ayrıca bahsi geçen frekans bölgesinde çalışmaya müsait ölçü aletlerinin temin olanaklarına göre, yine tasarlanan çıkış katının sürdüğü, tümdevre üzerine yerleştirilecek RF-pad yardımıyla çıkışların, "RF Probe Station" aracılığıyla gözlenmesine çalışılacaktır. Frekans sentezleme çalışmalarının amacı 40Gbps optik haberleşme standardına uygun saat işaretleri üretebilmektir. Bölüm-2.5'te anlatılan, DLL'in farklı uygulama alanlarında sağlaması gereken performans kriterleri hesaba katılarak, bahsi geçen çözümlerden hangisinin veya hangilerinin seçileceğine karar verilecek ve prototip tümdevresi son haline getirilecektir. Ayrıca DLL'in çevrim bandgenişliğinin gürültü performansına etkilerini gözlemleyebilmek amacıyla, çevrim filtresini oluşturan kapasite elemanı ve yük pompası kuyruk akımı değerleri prototip tümdevre dışarısından kontrol edilebilir hale getirilmiştir. DLL'e ek test devreleri detaylı olarak bölüm-5'te anlatılmıştır.

DLL seriminin tamamlanmış olmasına rağmen, bahsi geçen test bloklarının çıkışlarında ver alacak sürücü devre çözümleri ve paket seçimi üzerinde yapılan çalışmaların halen devam etmesi ve izin verilen silikon alanının henüz belirli olmaması sebebiyle, prototip tümdevresinin üst seviye birleşimi henüz tamamlanamamıştır. DLL'i oluşturan blokların seriminde, simetri önplanda tutulurken, yüksek frekanslı işaret taşıyan hatlar arasında kuplai en az seviyeye indirgenmeye çalışılmıştır. Önemli bir diğer husus ise, tümdevre üzerindeki sıcaklık gradyanı olduğundan, herbir altblok kendi içerisinde 1W/1mm<sup>2</sup> oranı uvarınca serilmiştir. Besleme ve taban zıplaması (V<sub>DD</sub>/Ground Bounce) olarak, devrelerin kuyruk akımlarını anahtarlaması sebebiyle ortaya çıkan gürültüden sistemin en az seviyede etkilenmesi için herbir alt devre için besleme akım çevrimini en kısa yapacak biçimde beslemeler arasında kuplaj kapasiteleri kullanılmıştır. Ayrıca besleme hatları herbir metal katmanda dağıtılarak, beslemeler arası parazitik kapasitesinin arttırılmasına çalışılmıştır. Diferansiyel işaret hatları, ortak işaret eşitliğini muhafaza etmek üzere uçları arasındaki kuplaj arttırılacak biçimde mesafelendirilirken, tabana yaptıkları parazitik kapasite ve hatların kendi parazitik dirençleri en aza indirilmeye çalışılmıştır. Bu amaçla dört adet metal katmana sahip prosesin en üst metal katmanı beslemelere ayrılmış, yüksek frekanslı saat isareti bir alt seviye olan metal-3 katmanından taşınmıştır. Metal-1 ve metal-2 katmanları ise alt blokların iç bağlantıları ile beslemelerinde kullanılmıştır. Özellikle üst seviye birleşim yapılırken, uzun hatların sonlarında yer alan emetör izleyici devrelerin, uzun hatların olası büyük parazitik dirençleri sebebiyle çınlama yapmaları engellenmeye çalışılmaktadır. Besleme hat genişlikleri, hatlardan çekilen akım değerleri uyarınca arttırılarak ve simetrik dağıtılarak, beslemelerde oluşacak parazitik I×R düşmesi en aza indirgenecektir.

DLL'in gürültü performansını büyük ölçüde belirleyen blok olduğundan, tek başına bir VCDL ürettirilmiştir. Test amaçlı olan ve DLL çevrimi içerisinde bulunmayan oniki katlı bir VCDL ve aynı VCDL'in ring-osilatör konfigürasyonu, tasarımda kullanılan 0.35µm SiGe BiCMOS prosesin önceli bipolar eşleniğinde ürettirilmiştir. VCDL, gürültü özelliklerinin ölçülebilmesi, ring-osilatör konfigürasyonu ise kontrol gerilimi ile çıkış frekansının değişiminden faydalanılarak, VCDL'in gecikme kontrol karakteristiği dolaylı olarak ölçülebilmesi amaçlarıyla ürettirilmişlerdir. Yardımcı ring-osilatör konfigürasyonun gürültü mekanizması VCDL'den farklı olduğundan, VCDL gürültü karakteristiğinin çıkartımına yardımcı olamayacaktır. Bu blokların çeşitli ölçüm düzenekleri ile karakterize edilmesi, hazırlanmakta olan prototip tümdevresi için önemli ölçüde yararlı olacaktır. Bu iki bloğun ölçüm çalışmaları halen devam etmektedir ve bölüm-5'te açıklanmıştır.

#### 1 INTRODUCTION

#### 1.1 Motivation

Delay Locked Loops (DLLs) become more popular circuit technique in modern electronic communication systems. As the name of DLL itself suggests, it is a feedback system that controls the delay of the ingoing signal and locks its output to the input with a constant amount of phase difference (usually zero) that allows eliminating the unwanted phase differences ("skew") in synchronizing signals, such as clock signal, and circuits those using clock signals, would work synchronized with each other, which is called "skew cancellation". This feature makes the DLLs' main application area, synchronization of dynamic digital circuits, in DSP (Digital Signal Processing) chipsets and microprocessors. Phase Locked Loops (PLLs) are also commonly used in this manner [Johnson, M. and Hudson, E., 1988], but higher noise immunity, inherently stable nature and so easier implementation of DLLs with respect to the PLLs make them more attractive in skew cancellation applications [Liu, A. and Lee, J., 1999].

Well known circuit techniques could be applicable to DLLs working on clock signals at megahertz frequency range, either in skew cancellation or frequency multiplication or clock/data recovery (CDR) or time-to-digital converter or symbol synchronization applications. Last couple of years, researches have been focused on exploiting DLLs' noise properties in some applications with different circuit techniques and DLLs working on hundreds of megahertz's had been demonstrated.

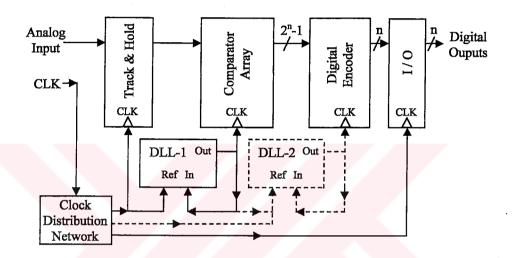

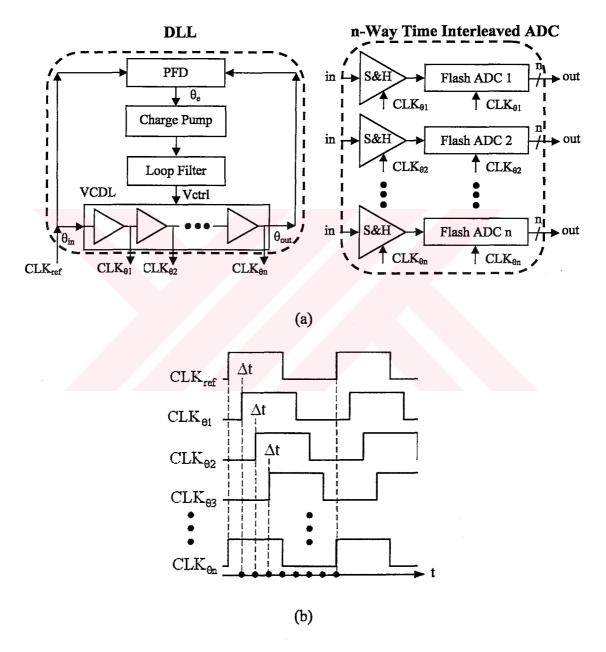

In mixed signal applications such as data converters, in addition to the skew cancellation, multiphase clocking (not only quadrature clock signals) allows paralleling the processes. Especially, Time-Interleaving topologies which have equal or more than 2 ways are widely used in low/moderate resolution and high speed Analog-to-Digital Converters (ADCs) which accommodate samplers (Sample&Hold or Trach&Hold circuits) requiring low jitter evenly spaced clock signals.

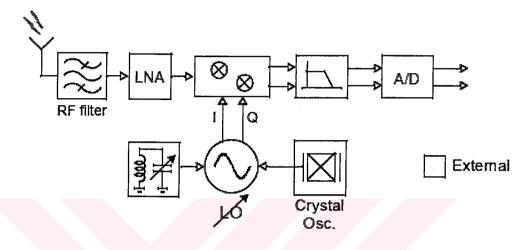

Transceivers in communications electronics generally use PLL based local oscillators (LOs), containing ring oscillator VCO or less noisy LC VCO [Razavi, B., 1998]. But increasing demand in higher carrier frequencies in newer applications, either wired or wireless, tightens the phase noise specification of the LOs. Excellent phase noise behavior of DLLs with respect

to the ring oscillator PLLs could make them major LO topology in a couple of years although its' low frequency multiplication factor. Frequency synthesizer DLLs, mainly accommodate a core DLL working on hundreds of megahertz range and different kinds of frequency synthesizer "Edge Combiner" circuitries with the output frequency up to 1.8 GHz for GSM applications [Chien, 2000], [Foley, D. and Flynn, M., 2000] and also a modified version of DLLs as a frequency synthesizer, called re-circulating DLLs [Ramin, F. and Dally, W., 2002] which could be considered as a combined version of DLLs and ring oscillator PLLs, had been demonstrated.

#### 1.2 Goals

Skew canceller DLLs operating at low frequencies and frequency synthesizer DLLs operates at higher frequencies, implemented in modern CMOS technologies, had a core DLL working on up to a couple of hundred megahertz had been demonstrated. Also DLLs producing multiphase clock signals for over giga sample per second time-interleaved ADCs working on same frequency range (a couple of hundred megahertz) could be seen on some products such as high speed sampling oscillators.

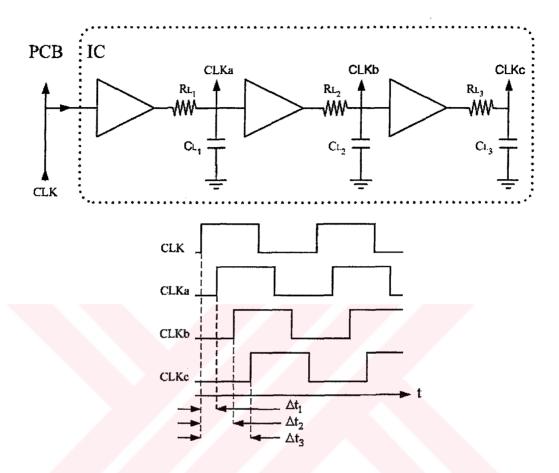

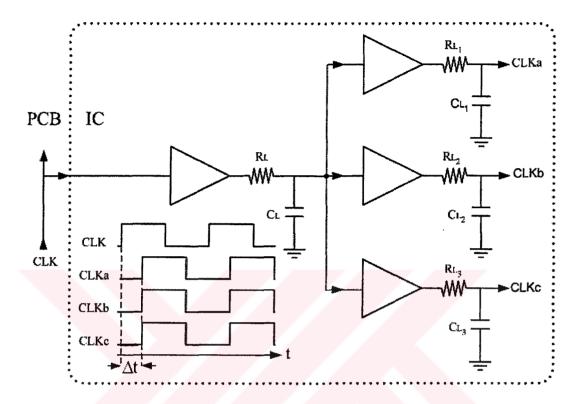

Clock distribution on modern ICs could be problematic while dealing with over a few megahertz clock signals. Some layout techniques for clock distribution such as H-tree mainly rely on achieving almost same amount of line length so each clock line sees almost same parasitic line resistances and capacitances although these lines take place in different portions of the IC. As the clock frequency increases, distributed behavior of parasitic elements and parasitic line inductances could be problematic and low timing budgets for synchronization at higher frequencies makes basic layout techniques incapable of solving skew phenomenon. Especially distribution of the over gigahertz range clock signals and synchronization of some even cascaded circuit blocks is a challenging matter.

Wired 10Gbps - 50Gbps communication systems, using laser pulses or stand-alone LC oscillator clock sources, require high speed circuit techniques (such as interleaving, downsampling) and/or high speed devices such as SiGe, GaAs, InP HBTs and HEMTs. Clock generation for these applications is another challenging matter and so frequency multiplication techniques using DLL and circuit techniques dealing with those high frequencies should be developed, designed and carefully characterized in order to compare different frequency synthesizer solutions.

This work focuses on "A 4GHz DLL Implementation" which could be mainly used as a skew canceller. DLL also could produce 6 evenly spaced 4GHz clock signals, which could be used in a 6 way Time-Interleaved ADC resulting equivalent sampling rate of 20-25Gsps. DLL design is based on 0.35µm SiGe HBT BiCMOS process parameters. After designing the 4 GHz DLL, two different edge combiner implementation approach (LC tank and OR/AND logic) for frequency multiplication techniques are investigated and designed in order to compare them. High speed circuit techniques for MOS and HBT devices were also investigated throughout the work in order to deal with up to 30GHz clock signals.

#### 1.3 Thesis Organization

The goal of the thesis is to review the theory of PLLs and DLLs, design and analysis of DLL circuits and a complete implementation of 4GHz SiGe HBT DLL for Skew Cancellation and Multiphase Clocking and also investigation of frequency synthesis of 20GHz-30GHz clock signals.

Chapter 2 presents basic description of DLLs and its loop components. Also this chapter gives some examples of DLL application areas and discusses over gigahertz range ICs system design problems.

Chapter 3 explains both s-domain and z-domain DLL models in order to describe the loop dynamics and noise behavior of DLLs.

Chapter 4 is the major subject of the thesis. A 4GHz SiGe HBT DLL design strategies, design steps, simulation results of the system will be presented.

Chapter 5 deals with the implementation problems, additional test circuits and measurement.

#### 2 DLL BASICS AND LOOP COMPONENTS

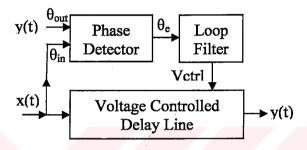

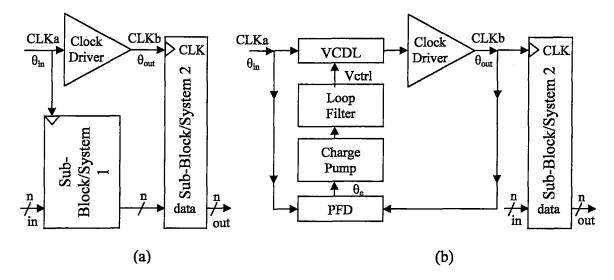

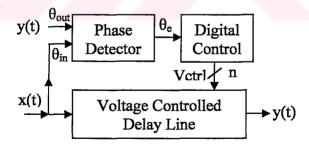

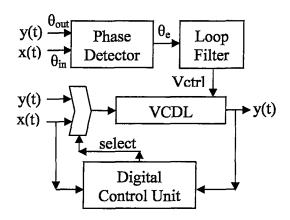

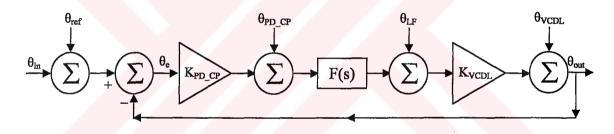

Delay locked loop is a feedback system that produces an output signal with zero phase difference with respect to its reference signal. DLL has three basic components (Figure 2.1);

- 1. A phase detector,

- 2. A loop filter,

- 3. A voltage controlled delay line.

Figure 2.1 Basic DLL block diagram.

The phase detector compares the phase of the input signal, x(t), against the phase of the VCDL output signal, y(t). Output of the phase detector is a voltage proportional to the phase difference between its two inputs. The loop is considered "locked" if the phase difference is constant with time. The loop filter filters out the phase difference voltage at the phase detector output. Loop filter is a lowpass filter, which suppresses the high frequency signal components and noise. Output of the loop filter is applied to the VCDL as the control voltage, Vctrl. This control voltage changes the delay of the VCDL in a direction that reduces the phase difference between the input signal, x(t), and the output signal, y(t). When the loop is locked, the control voltage is such that the output phase of the VCDL is exactly equal to the phase of the input signal; however, there may be a static phase error present. This error tends to be small in a well-designed loop.

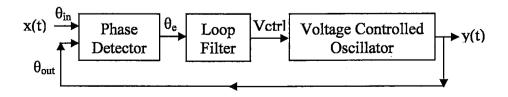

Figure 2.2 Basic PLL block diagram.

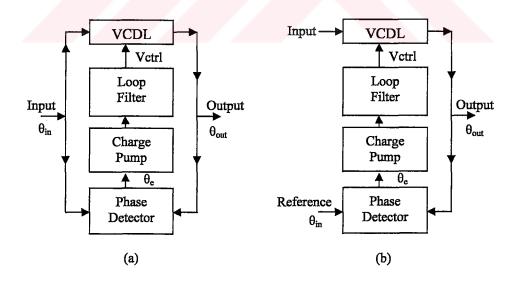

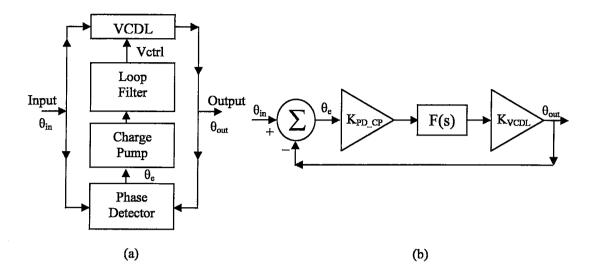

DLLs generally built up with same building blocks of PLLs as shown in Figure 2.2, but one major component, that is; voltage controlled oscillator (VCO) used in PLLs is replaced with voltage controlled delay line (VCDL). VCOs of PLLs oscillate in a predetermined frequency range. Oscillator output frequency is adjusted according to the phase and/or frequency difference with respect to the reference signal and the loop locks this output signal to the reference input. In DLLs, the loop locks reference input signals phase to its delayed versions phase at the output of the VCDL. PLL's output frequency need not to be the same as the reference input frequency because built in VCO can oscillate at a higher frequency with respect to the reference. In this case, frequency dividers could take place in feedback path of PLLs to reduce the VCO output frequency to the same value that of the reference in order to make a comparison. This makes PLL attractive in frequency synthesizers because large multiplication ratios could be achieved by the aid of frequency dividers. But VCDLs in DLLs just buffer its input to the output, with controllable phase difference. So the reference input and output of DLL are at the same frequency. But if VCDL is constructed with equal delay stages, it contains equally divided phases of the one period of reference signal, which gives an opportunity for multiplication, by properly combining these different phases of the reference signal. Naturally, the number of delay stages used in VCDL directly determines multiplication ratio and of course unequal delay stages or different implementation methodologies (such as passive, T-line) in VCDL could prevent frequency multiplication.

Loop components of DLL are almost same as those of PLLs. But it is important to keep in mind that PLL based frequency synthesizers generally consist of frequency dividers so PLL's comparison frequency at the inputs of the phase detector is much lower than the output frequency. This attribute makes loop components in PLLs, except VCO, easier to implement with well known circuit techniques with desired characteristics. In contrast, DLL loop components has to work properly at much higher frequencies, cause of the nature of the DLL that the input and the output frequencies are the same.

There are different kinds of loop components which should be carefully chosen whose characteristics could be useful in different applications of DLLs and PLLs. Some major kinds of loop components and circuit techniques will be described briefly in following sections.

#### 2.1 Phase Detectors

Phase detector is a kind of comparator produces a DC output error signal,  $\theta_e = \theta_{in} - \theta_{out}$ , corresponding to the phase difference of the two inputs. Output of the phase detector could be written as;

$$v_e = K_{PD}.\theta_e \tag{2.1}$$

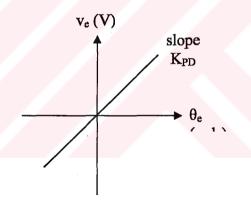

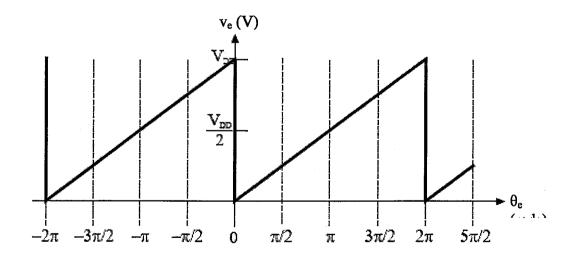

Where  $v_e$  is the DC output voltage,  $\theta_e$  is the phase difference between the input signals and  $K_{PD}$  is the phase-detector gain in volts per radian, V/rad. According to this definition, phase detector characteristic is linear in ideal case as shown in Figure 2.3. However, in practice the response of a phase-detector is generally nonlinear and repeats in a cyclic fashion over a limited phase range. The response is usually almost linear within a narrow phase difference range close to the point at which the loop will normally lock, and the slope of the characteristic, the phase-detector gain  $K_{PD}$ , is of most interest at this point.

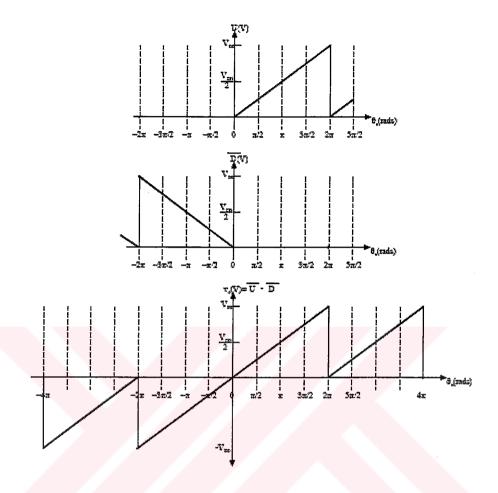

Figure 2.3 Phase detector characteristic in ideal case.

Phase detectors could be examined in two basic categories; multiplier type phase detectors and sequential phase detectors.

#### 2.1.1 Multiplier Type Phase Detectors

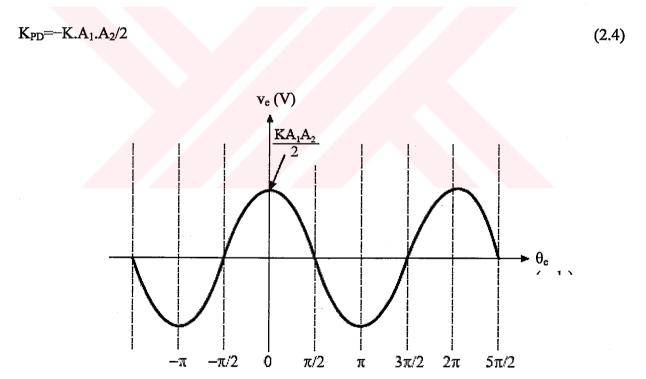

Multiplier type phase detectors could be understood as a basic analog multiplier. If the two input signal of the multiplier considered as sinusoids,  $x_1(t)=A_1.\cos(\omega_1 t+\theta_1)$  and  $x_2(t)=A_2.\cos(\omega_2 t+\theta_2)$ , the output of the multiplier  $v_e(t)=K.x_1(t).x_2(t)$  could be arranged as follows with aid of trigonometric manipulations;

$$v_{e}(t) = [\cos\{(\omega_{1} - \omega_{2})t + (\theta_{1} - \theta_{2})\} + \cos\{(\omega_{1} + \omega_{2})t + (\theta_{1} + \theta_{2})\}]K.A_{1}.A_{2}/2$$

(2.2)

where K is proportionality constant. It is clear that multiplier produces two frequency tones, difference and sum of input signals. In DLLs the two input signal of the phase detector has the same frequencies so first term of equation (2.2) became time invariant. The loop filter could filter out the second term of equation (2.2), which is at the summed frequency. And the output of the phase detector becomes proportional to the phase differences of the two input, recalling  $\theta_e = \theta_1 - \theta_2$ ;

$$v_e(t) = \cos(\theta_e) \cdot K \cdot A_1 \cdot A_2 / 2$$

(2.3)

Equation suggests that the phase-detector output varies sinusoidally with phase difference, with zeros at  $\theta_e = \pi/2 + n.\pi$  as shown in Figure 2.4. For zero error voltage, which means that the loop is locked, cosine term should be zero. This corresponds to  $\theta_e = \theta_1 - \theta_2 = 90^\circ$  phase difference, so multiplier type phase detectors has a static phase error of 90° in locked condition. From equation (2.3), adjusting the cosine term  $\cos(\pi/2 - \theta_e)$ , phase detector gain could be written as

Figure 2.4 Analog multiplier phase detector characteristic for sinusoidal inputs.

This types of phase detector could be useful in noise environments, because unwanted parts of the output signal could be removed and detector has no need to reference or threshold values which could be affected by the noise and degrades detection performance. Depending on the circuit topology, SNR values down to 10dB does not make the circuit malfunctions.

Phase detector exhibits a variable voltage slope and is monotonic. The phase detector gain is zero when the phase difference is zero, and is greatest when the input phase difference is 90°. Hence, to maximize the useful phase detection range, the loop should be arranged to lock to a phase difference of 90°. For this reason, a multiplier type phase detector is often called a quadrature phase-detector. Thus, although the phase difference is 90° in an ideal quadrature loop, the phase error is considered to be zero. The useable range of the detector, where the operation is approximately linear, is limited to within  $\pm \pi/4$  radians of  $\theta_e$ . So, the phase detector range is  $\pi/2$ . As could be seen from equation (2.4) phase detector gain is depended on input signal amplitudes, which is an undesirable attribute resulting input depended loop dynamics in DLL.

If one of the input signals of multiplier phase detector is square-wave rather than sinusoidal, linearity will improve and if both of the inputs are square-wave, besides linearity also capture range will increased too. But loop could react to the odd harmonics of the squared-wave at the inputs resulting false locking. In these situations, static phase error and input amplitude dependent gain are again problematic. Besides, linearity is strongly dependent on %50 duty cycle of the input signals. Further analysis about multiplier phase detectors could be found in [Pak, B., 2002]

Gilbert Cell and XOR phase detectors are well-known multiplier type phase detectors.

#### 2.1.2 Sequential Type Phase Detectors

Sequential type phase detectors operate only on the transitions of the input signals and therefore implemented in digital form. The sequential type poorly operates under low S/N conditions in which they exhibit a threshold effect. So, they are generally used at S/N ratios above 10dB. However, they can offer far superior capture and tracking performance. They can provide zero phase difference (or 180°) in locked condition and a constant gain over the entire operating range. Since they operate on the rising or falling edge, but not both, the phase-detector output has a ripple at the input frequency, which is difficult to suppress, and undesirable. However, operating only on one edge of the input signal makes the phase-detector characteristic independent of the duty cycle.

An important property of the sequential phase-detectors is; they produce a DC output even if the input signal frequencies are different, whereas multiplier phase detectors do not. Therefore, they also provide information about the magnitude of the frequency error. However being sensitive to edge transitions, a sequential phase-detector will misinterpret a missing edge as a frequency error and the loop will be forced to correct this error. So, they do not have the ability to flywheel. This behavior can be modified significantly. Sequential phase detectors can also be shown to produce harmonic lock voltages, but it is more difficult to generalize about sequential operations. However, tracing the waveforms of any specific sequential PD will quickly show its harmonic locking properties.

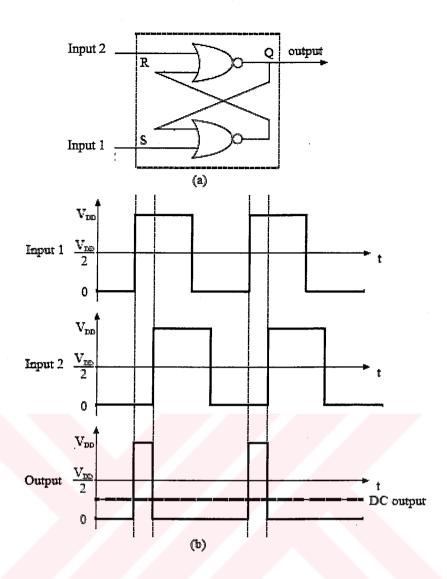

The simplest sequential phase detector is the set-reset (SR) flip-flop (Figure 2.5a). The flip-flop is set on the rising (or falling) edge of input-1 and is reset on the rising edge of input-2 as shown in Figure 2.5b. The ripple frequency is equal to the input frequency.

The mean DC output varies linearly between logic-0, when  $\theta_e$ =0 rad, and logic-1, when  $\theta_e$ =2 $\pi$  rads. The characteristic is plotted in Figure 2.6. This is the case for typical CMOS implementation, where the output swings from rail-to-rail, ground to VDD. The characteristic is sawtooth rather than triangular. In order to achieve a symmetrical output voltage swing, a DLL incorporating this phase-detector would lock at a phase difference of  $\pi$  rads. However, the DC offset of VDD/2 should be introduced at the loop-filter for the DLL to operate correctly. This phase-detector has a linear range of  $2\pi$  rads, which is twice that of an XOR phase-detector. So, it has an improved capture and tracking capabilities. The phase-detector gain is:

$$K_{PD}=V_{DD}/2\pi \tag{2.5}$$

The foregoing analysis assumes that the flip-flop responds equally fast to set and reset inputs. Any speed difference results in a static phase error. As a result something other than 180° phase difference is necessary to obtain an average output of VDD/2, if the set and reset operations take place at different speeds. Considering the typical SR flip-flop implementation in Figure 2.5a, this circuit has faster response to the reset than to the set input. Therefore, it is not appropriate for applications in which a small static phase error is important. Also, in the absence of an input signal the mean output latches-up in one state, preventing the detector from being used in CDR applications.

Figure 2.5 (a)SR flip-flop phase detector (b) SR flip-flop phase detector operation.

Figure 2.6 SR flip-flop phase detector characteristic.

It is mostly necessary to obtain lock with  $0^{\circ}$  phase difference. In such cases, an inverter may be added to one of the inputs of the SR phase detector to cancel nominally the 180° phase difference. However, the inverter delay now adds directly to the phase difference, and this is a serious problem particularly at high frequencies. As a result, SR flip-flop is not a suitable phase detector, if  $0^{\circ}$  phase error is necessary. Furthermore, it is often desirable to extend the phase detection range to span more than one period,  $2\pi$  rads.

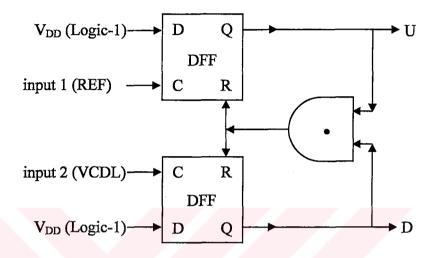

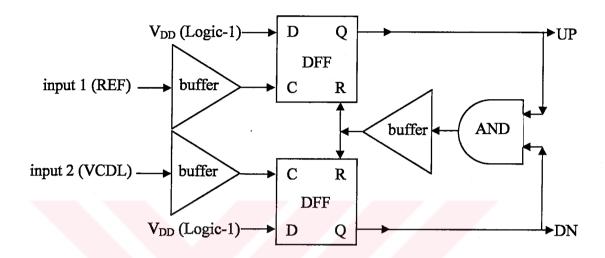

Figure 2.7 Phase/frequency detector.

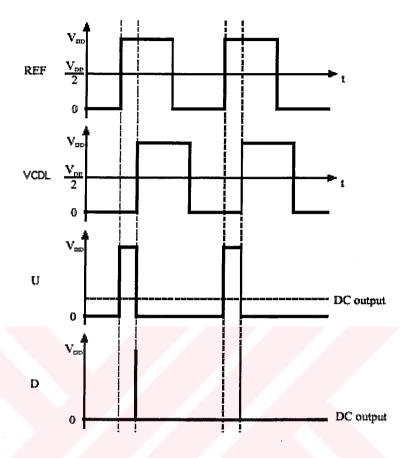

A more widely used type of sequential phase-detector is the phase/frequency detector (PFD) of Figure 2.7. It is constructed from a pair of D-type flip-flops and an AND gate. Data inputs (D) of the flip-flops are connected to logic-1 and the inputs are applied to the clock inputs of the flip-flops. The output of the flip-flop to which reference signal is applied is U which stands for "up". And the output of the flip-flop to which VCDL output signal had been applied is D which stands for "down". Up and down signals are inputs to an AND gate which drives the reset inputs of the flip-flops. Operation of the phase/frequency detector is illustrated in Figure 2.8.

Assuming that the input signal frequencies are equal and reference input leads VCDL output by an amount  $\theta_e$ , then after each rising edge of the reference, the U output is set to logic-1. When the rising edge of the VCDL output is received, for an instant both U and D outputs are set to logic-1. This produces a pulse at the AND gate output, the reset inputs, and then U and D outputs are set to logic-0. Ideally, we assume that the AND gate has zero response time. Thus, if the reference input leads the VCDL output, the mean value of the U output indicates the amount of phase lead, while the mean value of the D is virtually zero. Conversely, if the reference lags the VCDL output then the D output becomes active and indicates the amount of

the phase lag. Ideally none of the outputs, U and D, can be active at the same time. The difference of the mean values of U and D gives the phase/frequency detector characteristic.

Figure 2.8 PFD operation.

The output characteristic is given in Figure 2.9. It is a sawtooth characteristic with a linear range of  $\pm 2\pi$  ( $4\pi$ ) rads. So, the phase/frequency detector spans two periods. The phase/frequency detector gain is:

$$K_{PD}=V_{DD}/2\pi \tag{2.6}$$

which is the same as for the SR flip-flop. It is clear from the characteristic that to maximize the capture range, static phase error should be 0°. Also the DC output is zero for the lock point, which means that there is no need for DC offset compensation in the loop filter.

Time difference of up and down signals corresponds to the phase error of the two inputs. Theoretically the up and down signals zero in locked condition, therefore the output contain no spurious signals at all. In order to achieve this difference value an ordinary differential amplifier could be accommodated. While keeping in mind that these up and down pulses are at the same frequency of the input signal, the differential amplifier needs not to respond these pulses at high frequency but has to respond to the DC component. Usually a special form of

loop filter could be used to achieve these functions of both a differential amplifier and a loop filter, called charge pump, which will be explained in next section.

Figure 2.9 Phase/frequency detector characteristic.

There also exist different kind of sequential phase detectors like Bang-Bang (Hogge) phase detector, Alexander phase detector etc, used mostly in clock/data recovery applications with different characteristics [Razavi, B., 2002]. There also exist modified versions of phase detectors like "Precharged phase detectors" and many works have focused on phase detectors for different applications in recent years [Johansson, H., 1998]. But in this work, in order to distinguish leading or lagging output over two periods of reference input, phase/frequency detectors is of interest, which could distinguish not only the absolute phase difference, but also the phase relationship. From this point of view, PFD topology is selected as a phase detector and their partners charge pumps are of interest.

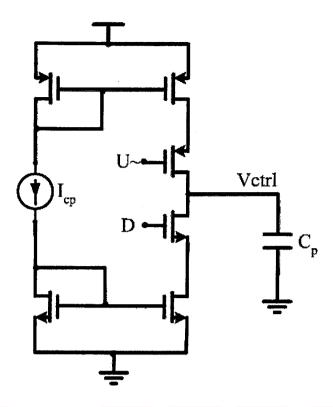

#### 2.2 Charge Pumps

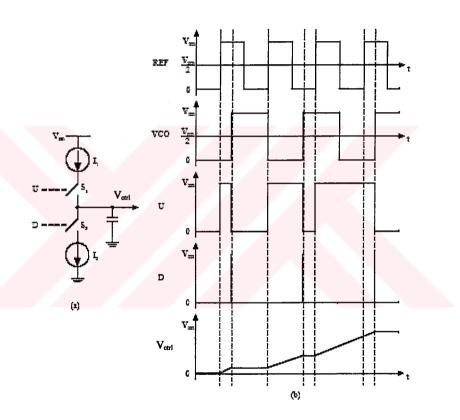

The charge pump could be understood by basic implementation consists of two switched current sources driving a capacitor (Figure 2.10a) [Gardner, F., 1980]. For a pulse width of  $\Delta t$

on U,  $I_1$  deposits a charge equal to I. $\Delta t$  on  $C_p$ . Or for a pulse width of  $\Delta t$  on D,  $I_2$  removes a charge equal to I. $\Delta t$  on  $C_p$ . Thus, if the reference signal leads the VCDL output, then positive charge accumulates on  $C_p$  steadily, yielding an infinite gain for the PFD.

Thus, the charge-pump introduces a pole at zero to the system. This is why; the charge-pump not only behaves as a differential amplifier but also as an integrating loop-filter. If pulses appear on D,  $I_2$  removes charge from  $C_p$  on every phase comparison, driving  $V_{out}$  toward  $-\infty$ . When U and D are both inactive, there is no net change on the charge;  $V_{out}$  remains constant (Figure 2.10b). The example is shown for PLL case here in order to be able to show the case for when reference and the output is at different frequencies.

Figure 2.10 (a) Charge Pump and (b) its operation

If the input signals have a phase error of  $\theta_e$  rads, then the average current charging the capacitor is given by:

$$I_{av} = I_{cp} \cdot \theta_e / 2\pi \tag{2.7}$$

and the average change in the control voltage is;

$$V_{ctrl}(s) = (I_{cp} \cdot \theta_e / 2\pi) \cdot (1/sC_p)$$

(2.8)

which can be written in general form of;

$$V_{ctrl}(s) = K_{PD}.\theta_{e}.F(s)$$

(2.9)

Thus, if we combine phase/frequency detector and charge pump, overall gain would be;

$$K_{PD\_CP} = I_{cp}/2\pi \tag{2.10}$$

and the loop filter transfer function is simply;

$$F(s)=1/sC_p$$

(2.11)

which is a perfect integrator's transfer function.

The most important problem of the PFD is the crossover distortion, changes in gain that occur near zero phase error. Assuming that the D-type flip-flop outputs exhibit relatively long transition times compared to the AND gate delay (reset-path delay), the reset is immediately activated when U and D exceed the threshold of the AND gate. The goal is to examine the increment in the charge deposited on  $C_p$  for an increment  $\Delta t$  in the delay between the input signals or simply the small-signal gain.

Figure 2.11 PFD dead-zone and corresponding DLL output peak-to-peak jitter.

The phase detector characteristic has a flat response near zero phase difference. This is called "dead-zone". The dead-zone is undesirable in a DLL because the loop is effectively opened (since K<sub>PD</sub> is zero) and the output spectrum changes accordingly. If the phase difference varies within the dead-zone, the DC output of the charge-pump does not change significantly and the loop fails to correct this error. Consequently, a peak-to-peak jitter approximately equal to the width of the dead-zone arises in the output. Figure 2.11 shows the relation between dead-zone of PFD and the phase error of the DLL. If the phase difference of the reference clock and the VCDL output is smaller than the dead-zone, the PFD cannot detect

the phase difference. The minimum peak-to-peak phase error caused by this dead-zone could be written as;

$$\theta_{e(pp)} = 2\pi T_{dead-zone} / T_{period}$$

(2.12)

To solve this phenomenon, it is obvious that the reset-path delay must be more than the flip-flops' transition delay. When the D output crosses the threshold, the reset signal is not asserted as a result of the extra delay. So, both outputs, U and D, continue rising and reach full logic level if reset-path has sufficient delay. They both stay at logic-1 for sometime and then return to logic-0 when the reset signal arrives. Thus, U stays at logic-1 more than D with a time equal to the phase difference. When both outputs are high, both switches are on and the net charge delivered to the output is zero. So, the net charge is completely defined by the phase difference between the inputs. Thus, the dead-zone disappears only if U and D outputs are simultaneously high for a sufficient amount of time. In lock, both U and D are simultaneously high for a time equal to the reset-path delay.

Another problem about charge pumps could arise from mismatches of current sources  $I_1$  and  $I_2$  and switches  $S_1$  and  $S_2$  in Figure 2.10a. Even if the phase difference is zero, control voltage will vary every comparison period because of mismatched current sources will deposit or remove charges from loop filter capacitance with an amount of  $I_1$ – $I_2$  (assuming  $I_1$ » $I_2$ ). This mismatch current will deposit charges to filter capacitance during reset-path delay time. So it is possible to write down control voltage ripple as;

$$\Delta V_{\text{ctrl}} = (I_1 - I_2) \cdot t_r / C_p \tag{2.13}$$

where  $t_r$  is reset-path delay. The current mismatch would cause reference sideband in the spectrum and the value of  $\Delta V_{ctrl}$  would directly determine the sideband levels.

Figure 2.12 Charge pump and loop filter implementation example.

Some practical charge pump implementation (Figure 2.12) problems could arise, for example if the current sources would be designed as MOS current mirrors (PMOS through the  $V_{DD}$  and NMOS through the ground), besides mismatches, current sources could not be able to supply desired current values if the control voltage reaches one of the supply rails. So enough voltage headroom has to be supplied to the current sources. These levels would be boundary for control voltage, so achievable amount of delay should be examined at these control voltage levels of VCDL. If the current sources leaves saturation and enough voltage headroom could not be supplied, this would degrade the gain of the block that would directly affect DLL, so that DLL loop dynamics should be carefully investigated under these circumstances.

If S<sub>1</sub> and S<sub>2</sub> switches were implemented as MOS switches and they were off, a recovery time necessary to go on. If this time longer than the phase difference, dead-zone phenomenon would appear. Also, when the switches are at off state charge injection and feedthrough mismatches would cause the control voltage to be disturbed. Parasitic capacitances also should be taken into account; those who are parallel to the loop filter capacitance would affect the calculated DLL bandwidth. Charge sharing mechanism around the filter capacitance and the other parasitic capacitances (for example; drains of current sources) would make control voltage to jump some value, which could cause reference sidebands at the output of the DLL.

Different kinds of implementation approach could be useful in order to solve current mismatching, device parasitic effects, fully turning on and off effects of the devices and others. For example, a differential charge pump could increase noise immunity. Also accommodating only one current source would completely remove current mismatch's unwanted effect to the DLL like spurious tones at the output.

#### 2.3 Loop Filters

Loop filters would directly affect the bandwidth of the DLL as will be explained in chapter 4. In contrast to PLL, DLLs are inherently stable so there is no need neither lag nor lead-lag nor different kind of filters, only a pole at zero is enough. This first order filter is only a capacitor at the output of the charge pump, as could be seen in Figure 2.12.

In special cases like jitter amplification phenomenon and some modified versions of DLL like re-circulating DLLs, second or more ordered filters could be necessary. But these are of concern at this time.

#### 2.4 Voltage Controlled Delay Line

Voltage controlled delay line (VCDL) is the most important part of the DLL because its performance dominates DLLs features such as capture range, inherent noise behaviors, spectral purity. Thus VCDLs could have the following characteristics in order to achieve a properly working DLL having advantageous noise behavior;

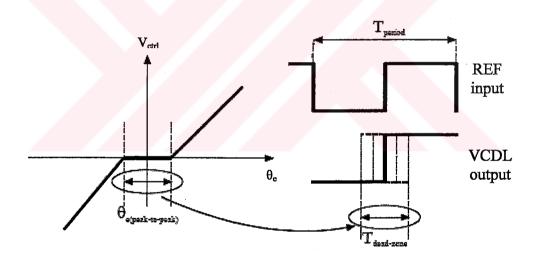

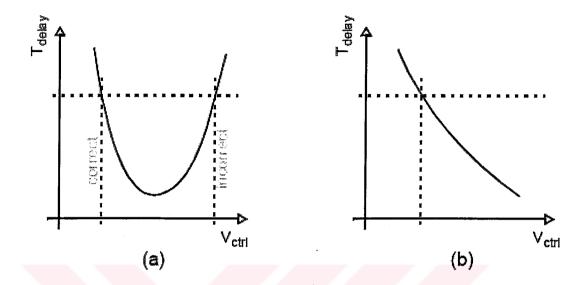

VCDL should have monotonic transfer function within the tuning range: VCDL's gain could be thought as the ratio of the output phase/delay and control voltage. Monotonicity means that only one delay value corresponds to a control voltage. This feature prevents DLL to lock to an incorrect state or to latch-up.

Figure 2.13 shows two possible transfer functions for DLL. If the VCDL having a transfer function like parabolic curve in the Figure 2.13a, it is possible that the loop could not be able to lock the output phase to the reference. This could be understood by considering a phase difference  $\Delta\theta$  between the reference and the output at the initial state. Phase/frequency detector would compute the absolute of phase difference and its direction (whether the output leading or lagging the reference) and the charge pump would produce a control voltage using phase/frequency detector output. So the feedback loop would increase or decrease the control voltage to add more delay (or decrease the delay) in order to approach the output to the

reference. But the transfer function like parabolic curve, loop could not be able to distinguish the demand on control voltage acts whether increase or decrease. So it is likely that VCDL total delay would stack to one of the extreme cases, meaning false locking to a state with a static phase error.

Figure 2.13 Some possible transfer functions for DLL

With the aid of transfer function seen in the Figure 2.13b, loop would determine direction whether increasing or decreasing the control voltage (so the VCDL's total delay) in order to achieve zero phase difference between output and the reference. Monotonic transfer function would avoid DLL to lock an incorrect state within the tuning range.

#### VCDL should have a controllable amount of delay at least equal to the reference period:

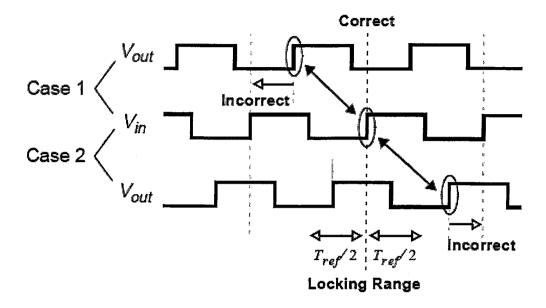

Although the phase/frequency detector used in this implementation determines the phase offset between input and output, it does not always match corresponding edges from the correct input and output pair. For instance, in Case 1 of Figure 2.14, if output is severely leading input by more than  $T_{ref}/2$ , the phase/frequency detector may determine that output is lagging the previous edge of input by less than  $T_{ref}/2$  and try to adjust the control voltage to speed up the VCDL even further. The opposite can also happen when output is severely lagging input by more than  $T_{ref}/2$ , shown in Figure 2.14, Case 2. Therefore, to avoid the above situation, signals presented at the phase detector inputs need to be within a certain range, ideally within  $\pm T_{ref}/2$ , to guarantee correct phase detection.

The total phase delay of the VCDL needs to be within  $\pm \pi$  of the reference period by design including PVT (process, voltage, temperature) variations. In general, VCDLs are designed to have controllable delay more than one period of the reference and even equal to two periods

of the reference. But under this circumstance this feature should be handled carefully by startup conditions of the loop and control logic, determining which edge to be locked.

Figure 2.14 Phase difference detection range

Delay stages forming VCDL should be identical: Firstly, this feature is not valid for passive implementation of VCDL, for example transmission line with tunable phase shift along the delay line and also for active implementations for DLL used in skew cancellation applications. Because feedback loop compares only the output of the VCDL, not any of inner nodes, with reference and locking occurs for the output phase. But application areas of multiphase clocking and frequency synthesizing, inner nodes of VCDL containing different phase shifted versions of the reference, carry useful information. These applications rely on the equally divided phase shifts of reference period. In order to exploit DLLs different application areas, each delay cell need to have identical phase/time delay and to be adjusted uniformly.

This feature lowers the levels of spurious tones at the output of the frequency synthesizer or interleaved processing units. Also using identical delay stages brings design simplicity for the VCDL.

### 2.4.1 Delay Stages

Voltage controlled delay lines could be constructed from basic delay elements called "delay stages (=delay cells)". Simply, a delay stage adds some constant delay and a controllable delay to its ingoing signal. It is not always possible to achieve desired controllable amount of

delay with one stage. In order to achieve enough adjustable delay and characteristics listed above, VCDL could be formed from number of delay stages. Also, multiphase clocking requirements or frequency multiplication factors could dictate the number of delay stages in the VCDL.

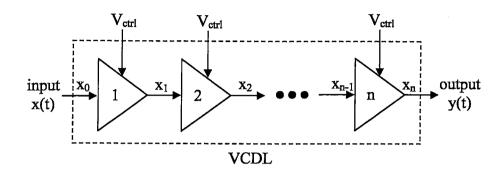

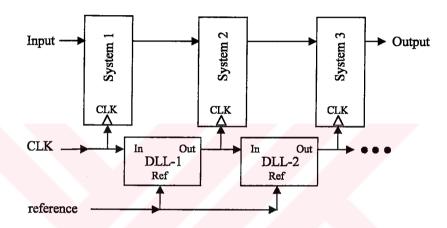

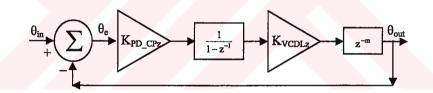

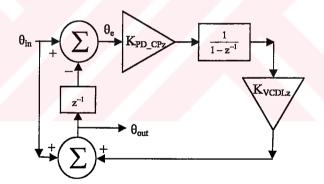

Figure 2.15 Voltage controlled delay line block diagram.

Figure 2.15 shows VCDL block diagram built up "n" delay stages. Each stage could be thought as buffer stages with control input. VCDL could be designed as to have a delay of multiple of reference frequency period, m×T<sub>ref</sub>. In locked condition, output and input of the VCDL would be in-phase. If m=1, each buffer output would be evenly spaced in reference frequency period, x<sub>1,2..,n</sub>. so T<sub>ref</sub>/n spaced multiphase clock signal were available for interleaved processing. And also these signals could be used in frequency multiplication and multiplication factor would be equal to number of delay stages, n. Value of m could also be more than one, and so VCDL could output multiple of reference frequency period divided by number of delay stages, n. In general, frequency multiplication factor or multiphase clocking factor would be;

$$F=T_{ref}.m/n$$

(2.13)

If "m" is greater than one, DLL dynamics should be carefully investigated in discrete time domain, because stability problems could occur. Defining number of delay stages, n, relies on implementation issues and application area of DLL.

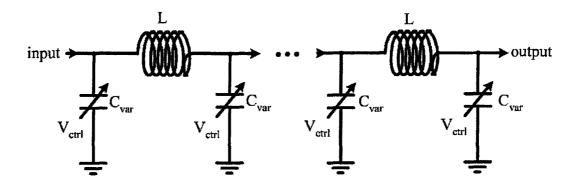

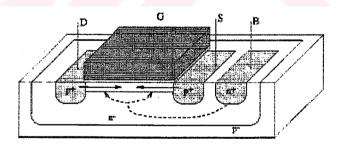

As mentioned before, VCDL could be constructed with passive devices and transmission lines. These methods could prevent multiphase clocking and frequency multiplication features of the DLL if only one stage operating as VCDL. In Figure 2.16 a simple implementation example had been shown. An on-chip inductor and a capacitor could be used to form a resonator. Varactors could be implemented as variable capacitor to tune the phase shift of the stages. Numbers of resonant stages could be used in VCDL in order to get the advantage of

multiphase reference signal. Passive VCDL would result better noise performance with respect to active devices. On-chip inductors occupy large silicon area and low quality factors (Q) and very low matching properties make this solution unfeasible.

Figure 2.16 Passive implementation of VCDL.

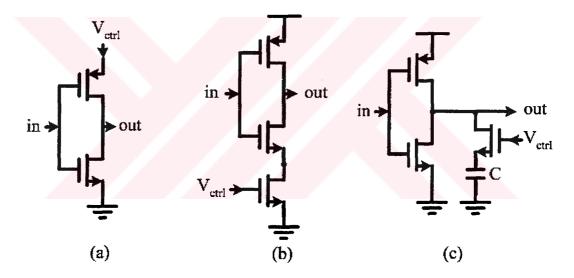

Figure 2.17 Implementation examples of single-ended delay stages.

Active buffer stages and inverters are widely used in DLL applications as delay stages. In Figure 2.17 some CMOS implementation examples had been shown. Each of the circuits has different delay setting mechanisms. First, adjusting positive supply would speed up or down the inverter stage. Second, adjusting tail current would again control the delay of the inverter and third, adjusting the capacitive loading of the inverter and so delay of the stage (note that capacitor C, could be implemented as NMOS capacitor connecting source and drain terminals to the ground and adjusting the AC capacitance seen from the gate terminal). These circuits are widely used in megahertz range DLLs occupied in digital circuits. But as the operating frequencies increase their supply noise sensitivity and speed limitation of CMOS devices

make them useless (in deep sub-micron processes speed limitation could be overcame). Interstage gain considerations are also important in these implementations, changing voltage gain of the stages, affects rise/fall times of the signal resulting jitter.

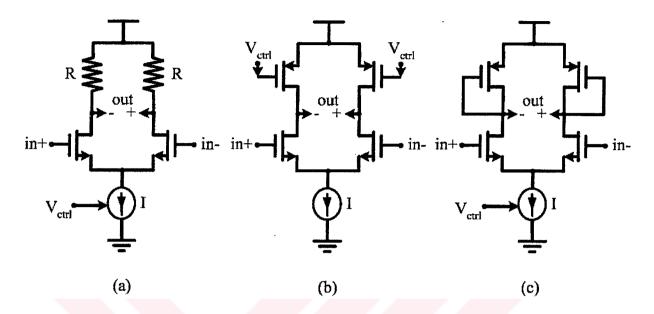

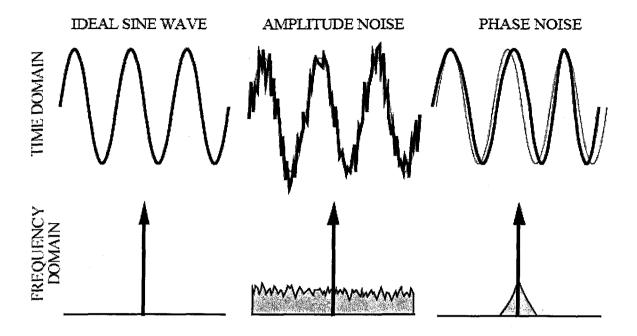

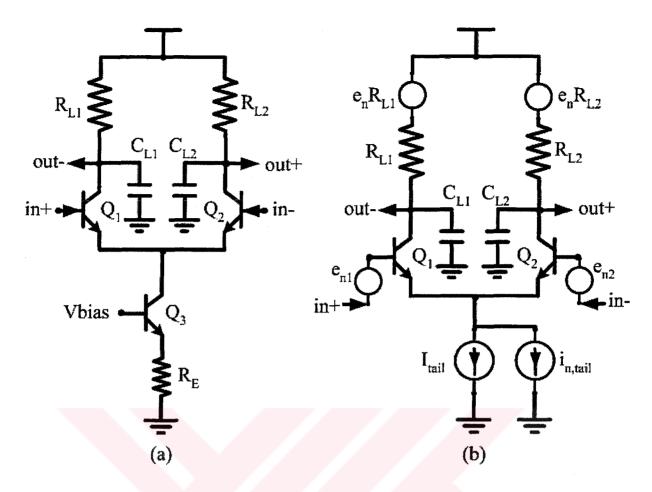

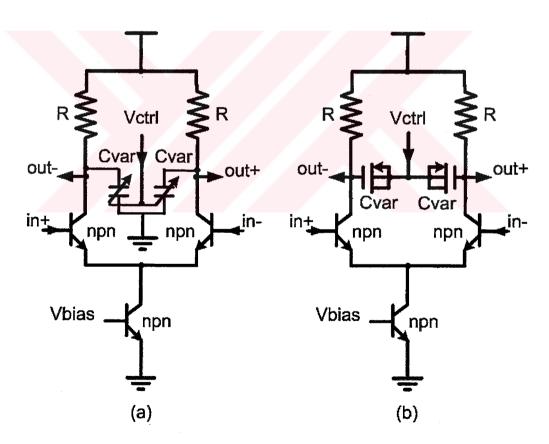

Figure 2.18 Implementation examples of differential delay stages.